3月26日消息,韩国媒体 BusinessKorea 报导指出,韩国三星电子于 2022 年 12 月成立了先进封装(AVP)部门,负责封装技术和产品开发,目标是用先进的封装技术超越半导体的极限。而三星 AVP 业务副总裁暨团队负责人 Kang Moon-soo 日前指出,三星将藉由 AVP 业务团队,创造现在世界上不存在的产品。

3月10日消息,据韩国媒体BusinessKorea报导,三星为发展先进封装技术,已挖来台积电前研发副处长林俊成,担任半导体部门先进封装事业副总裁。产业专家认为,这显示三星希望在各方面都能追赶台积电的企图心,不过,短期内仍难以撼动台积电领先地位。

1月5日,长电科技宣布,公司XDFOI™ Chiplet高密度多维异构集成系列工艺已按计划进入稳定量产阶段,同步实现国际客户4nm节点多芯片系统集成封装产品出货,最大封装体面积约为1500mm²的系统级封装。

11月11日消息,据外媒theregister报道,芯片互联初创公司Eliyan于 8 日宣布,已获得英特尔、美光风险投资部门等投资人的4000万美元投资。

9月26日消息,据路透社援引两位知情人士的爆料指出,意大利即将卸任的总理Mario Draghi 与其政府团队和处理器大厂英特尔(Intel)商定,将意大利东北部威尼托大区(Veneto) 的维加西奥镇(Vigasio)作为英特尔新半导体工厂的优先地点。

8月24日晚间,通富微电发布2022年半年报。报告期内,公司公司实现营业收入95.67亿元,同比增长34.95%;归属于上市公司股东的净利润3.65亿元,同比下降8.84%。

8月18日上午,易卜半导体年产72万片12吋先进封装产线项目启动仪式在上海宝山区顾村镇机器人产业园举行举行,项目预计2023年第三季度试产,第四季度实现量产。

近日,长电科技宣布,公司在先进封测技术领域又取得新的突破,实现4纳米(nm)工艺制程手机芯片的封装,以及CPU、GPU和射频芯片的集成封装。

虽然在半导体先进制程工艺方面,近日三星成功抢先台积电量产了3nm GAA制程工艺,但是在2.5/3D先进封装技术方面,三星仍落后于英特尔和台积电。而为了缩短这方面的差距,三星也已经组建了新的半导体封装工作组发力先进封装技术。

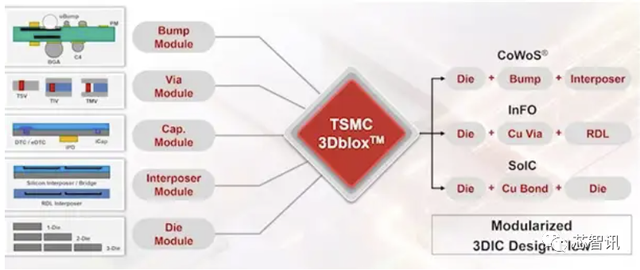

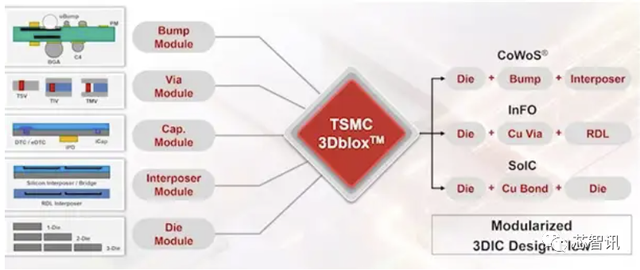

当地时间6月16日,晶圆代工巨头台积电在美国加利福尼亚州圣克拉拉召开了2022年台积电技术研讨会,介绍了台积电的技术现状和即将推出的路线图,涵盖了工艺技术和先进封装开发的各个方面。在之前的报道《台积电2nm细节曝光:功耗降低30%!成熟制程产能2025年将提升50%》当中,我们有介绍关于制程工艺技术的部分。今天我们再来聊聊台积电的先进封装技术。

6月24日消息,台积电今天宣布,子公司台积电日本3D IC研发中心,位于日本产业技术综合研究所的筑波中心完成无尘室工程,并在今天举行开幕仪式

6月2日消息,半导体封测龙头日月光宣布,推出垂直互连整合封装解决方案——VIPack 先进封装平台。VIPack 是日月光扩展设计规则,并实现超高密度和高性能设计的下一世代3D 异质整合架构,此平台利用先进的重布线层(RDL) 制程、嵌入式整合以及2.5D/3D 封装技术,协助客户在单个封装中集成多个芯片来实现创新未来应用,目前该平台已经正式推向市场。