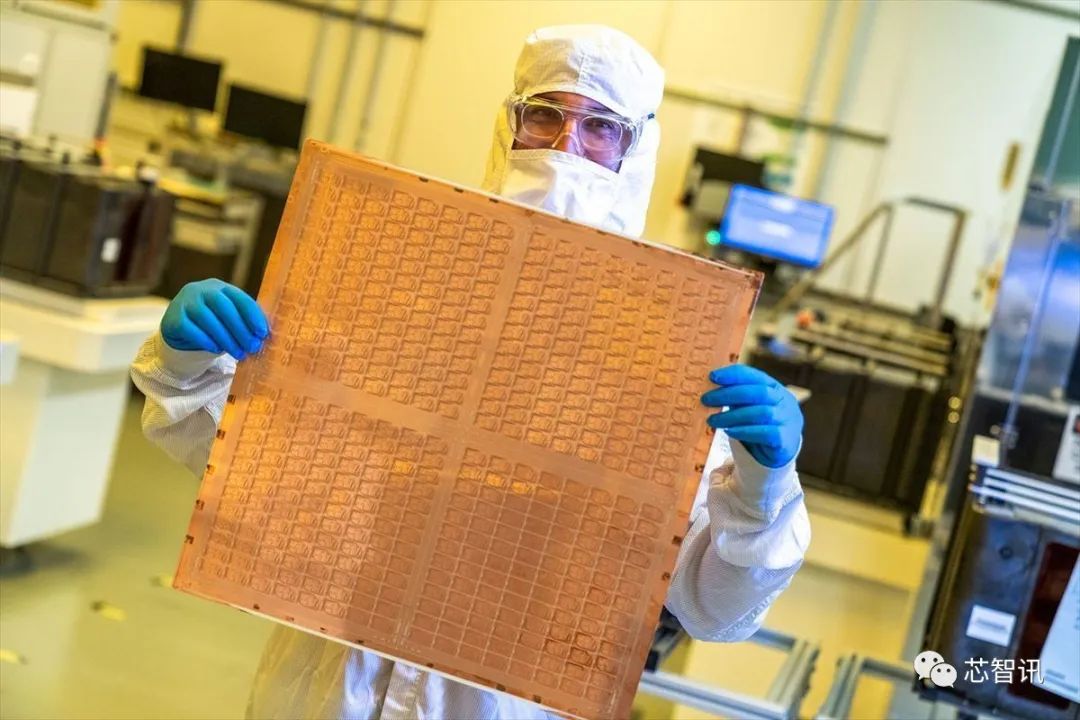

当地时间9月18日,英特尔对外披露了其半导体玻璃基板技术的开发进展,旨在助力英特尔实现在2030年前将单一封装芯片中的晶体管数量上限提高至1万亿个的目标。

9月7日消息,据台媒《经济日报》报道,台积电董事长刘德音昨日表示,当下AI芯片短缺问题,主要是因为CoWoS先进封装产能不足,台积电正尽力支持客户,预期一年半后技术产能可赶上客户需求,当前短缺应该是暂时、短期现象。此外,半导体技术发展“已抵达隧道的出口,隧道以外有更多可能性,我们不再受隧道的束缚”。

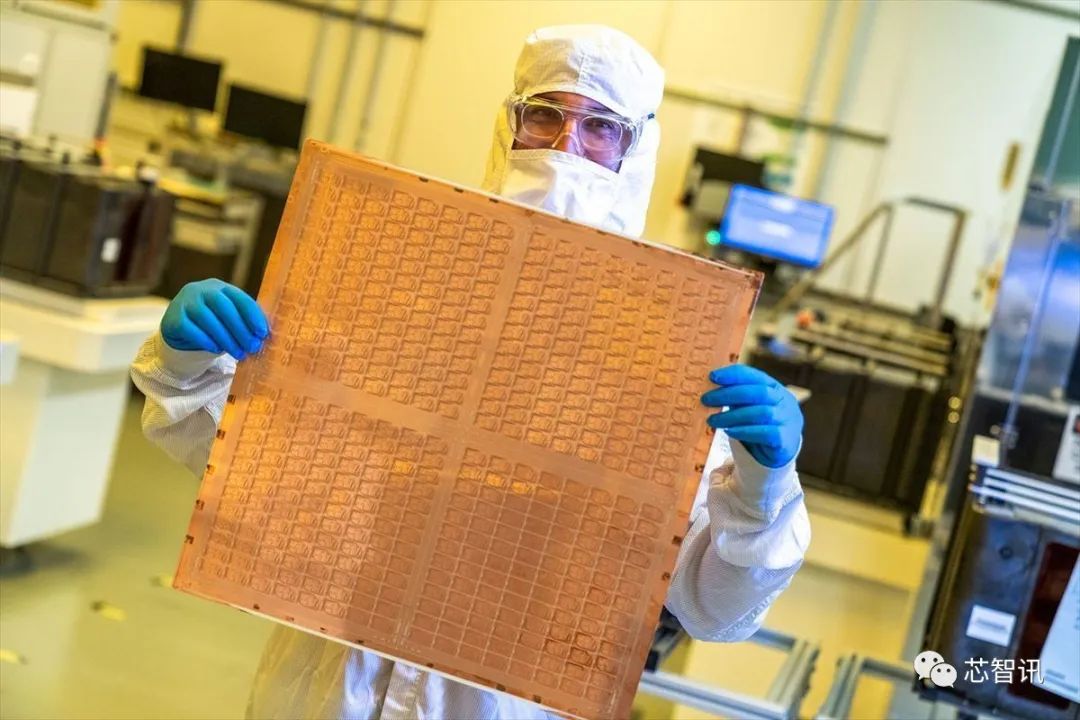

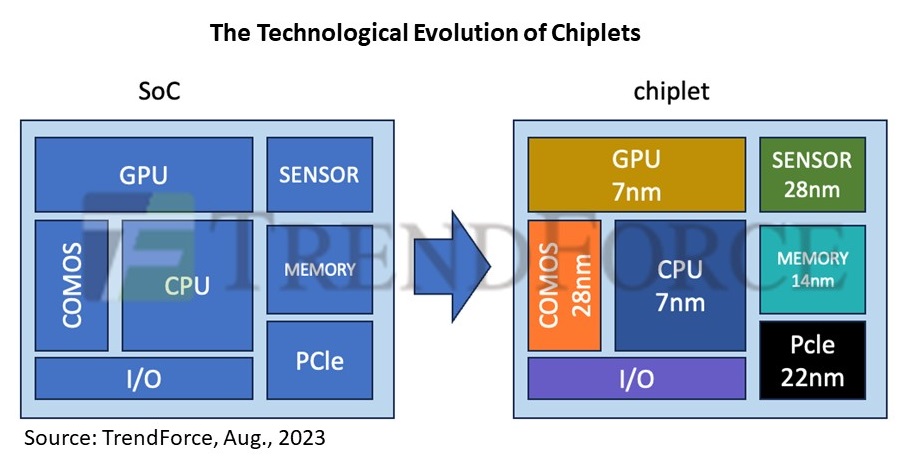

半导体制程技术逼近已知的物理极限,为了持续强化处理器性能,小芯片(Chiplet)、异质整合技术乃蔚为潮流,更被视为延续摩尔定律的主要解决方案,世界大厂如台积电、intel、三星等,都在全力开发相关技术。

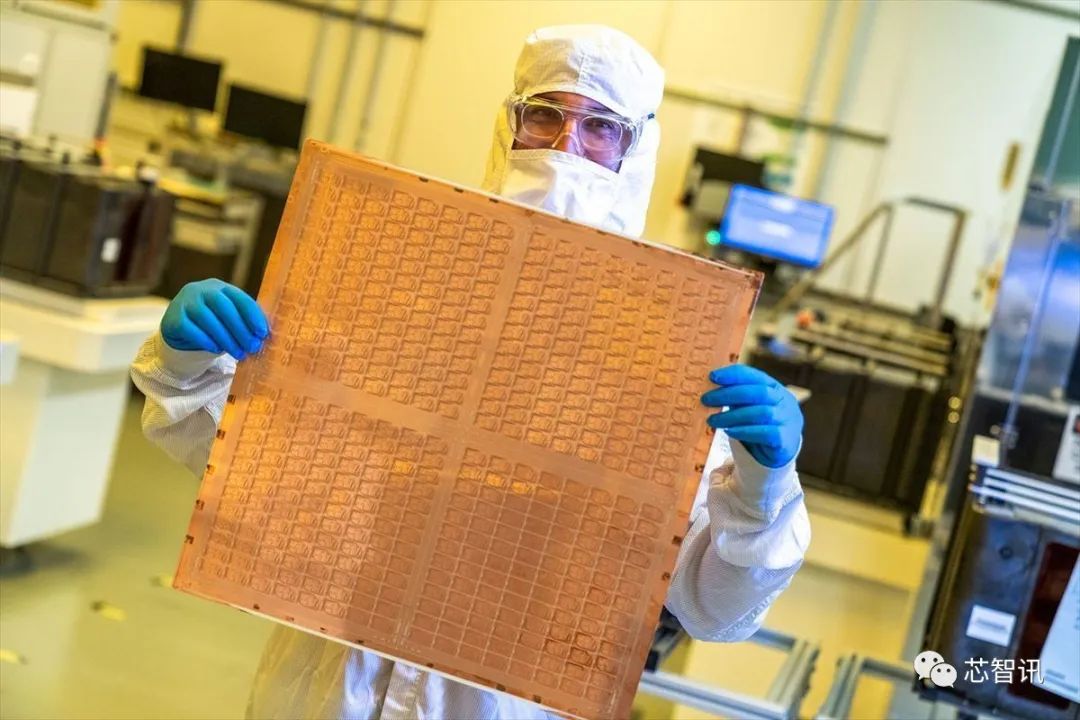

8月29日消息,英特尔为了满足当前在全球先进制程制造的布局,不久前宣布在已经有投资了 51 年历史的马来西亚扩增先进封装的产能,目标是在 2025 年将先进封装的产能较当前提升达4倍。

8月24日消息,英特尔目前在积极投入先进制程研发的同时,在先进封装领域也是火力全开。目前英特尔在马来西亚槟城兴建最新的封装厂,以强化其2.5D/3D封装布局版图,近日更是提出了2025年时,旗下最先进的3D Foveros封装产能将较目前大增四倍,并开放给外部客户单独采用。

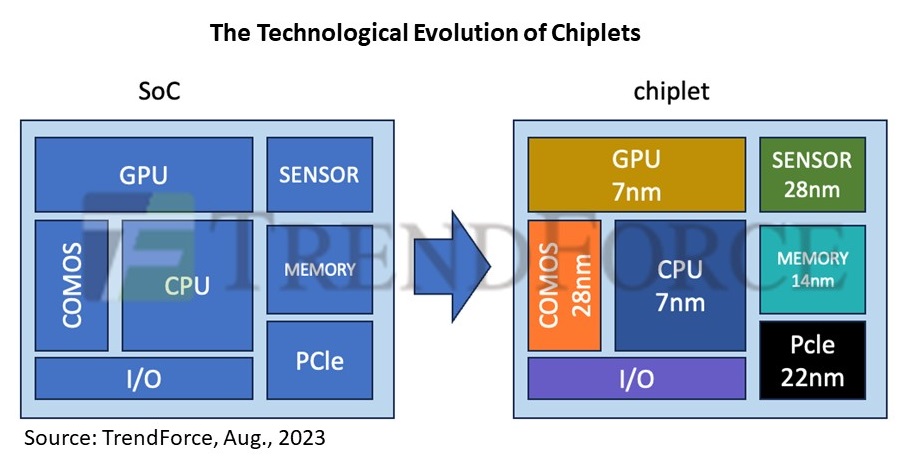

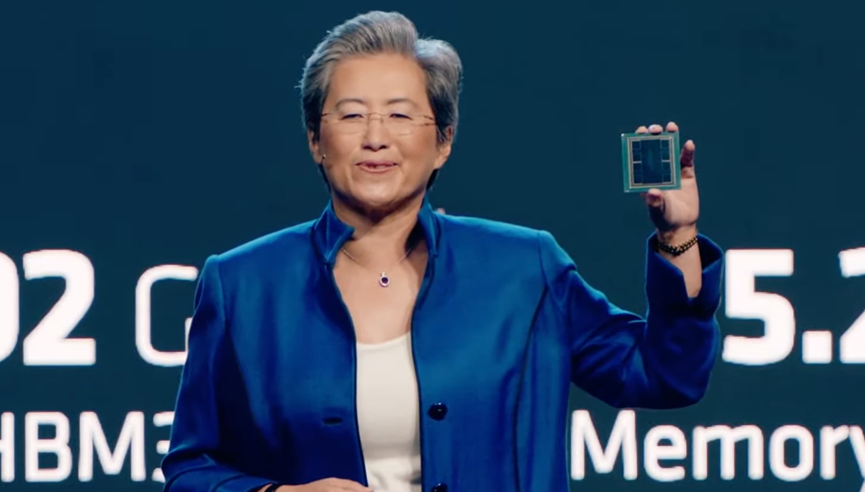

8月23日消息,据《韩国经济日报》22日引述业界消息报道称,三星的第四代HBM产品“HBM3”及先进封装服务最近已通过了AMD的品质测试。AMD的Instinct MI300系列AI芯片计划采用三星先进封装服务和HBM3。

为了满足高性能计算、AI、5G 等应用需求,高阶芯片走向小芯片(Chiplet)设计、搭载 HBM 高带宽内存已是必然,因此封装型态也由 2D 迈向 2.5D、3D。

过去数十年来,为了芯片的晶体管数量以推升计算性能,半导体制造技术已从1971年10,000nm制程升级至2022年3nm制程,逐渐逼近目前已知的物理极限。但随着人工智能、AIGC等相关应用高速发展,设备端对于核心芯片的性能需求将越来越高;在制程技术提升可能遭遇瓶颈,但是对算力需求持续走高的情况下,通过2.5D/3D先进封装技术提升芯片内部晶体管数量就显得格外重要。

8月7日,鸿海旗下夏普(Sharp)公司今天在东京举行半导体科技日活动,在下午举行三场讲座活动中,鸿海半导体策略长蒋尚义以“从集成电路到集成小芯片(From Integrated Circuits to Integrated Chiplets)”为主题发表了演讲。

8月5日消息,据英国《金融时报》报道,英国科技大臣Paul Scully近日在接受采访时表示,英国必须把重点放在先进封装和设计,而不是指望通过数十亿英镑的国家补贴和晶圆厂投资,来超越美国和中国等竞争对手,“英国芯片业无法在南威尔士(South Wales)再建造一个中国台湾”,因为人们担心英国没有承诺足够的投资来参与国际竞争。

8月2日消息,据韩国媒体BusinessKorea报导,有业内人士8月1日透露,三星积极争取英伟达(NVIDIA)的HBM3高带宽内存和先进封装订单,已进入技术验证阶段,验证通过后,英伟达将会向三星采购HBM3,并将部分高端GPU芯片H100的先进封装订单外包给三星代工。

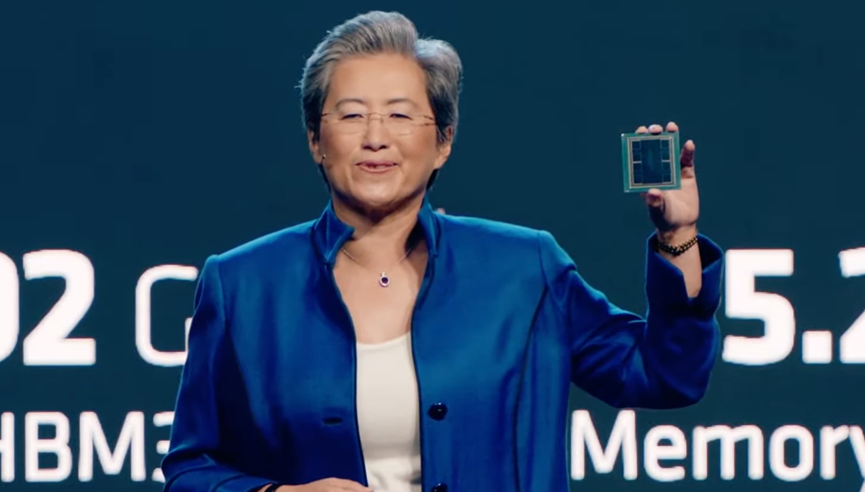

近日业内传出消息称,继AMD后,苹果也小量试产了基于台积电最新的3D小芯片堆叠技术的SoIC(系统整合芯片),规划采用台积电的SoIC 搭配 InFO 封装方案,预定面向 MacBook 使用,最快 2025~2026 年有机会看到终端产品问世。