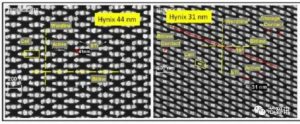

“尤其是随着10nm制程的临近,使其在晶圆上定义电路图案已经接近基本物理定律的极限。由于工艺完整性、成本、单元泄漏、电容、刷新管理和传感裕度等方面的挑战,DRAM存储单元的缩放正在放缓。”Techinsights分析师接着说。于是,正如报道中所说,行业正在寻找新的解决方案。

法国分析机构Yole也指出,即使通过光刻 EUV 工艺,平面缩放也不足以在整个下一个十年提供所需的位密度改进。因此我们迫切需要材料和架构方面的突破,以进一步扩展 DRAM,从而降低成本、最大限度地降低功耗并提高速度。而单片 3D DRAM(相当于 3D NAND 的 DRAM)已经被主要设备供应商和领先的 DRAM 制造商视为长期扩展的潜在解决方案。

按照Yole的预估,这种新颖的 3D 技术可能会在 2029-2030 年的时间范围内进入市场。韩媒businesskorea则强调,包括韩国三星、SK海力士以及美国美光在内的三大DRAM巨头正在加速3D DRAM的商用。

如下图所示,传统的DRAM 被组织为一组存储体,其中包括排列成行和列阵列的存储元件。存储器阵列以存储器子阵列的分层结构分组,以实现高效布线和降低功耗。每个存储单元都被建模为晶体管电容器对,数据作为电荷存储在电容器中。每个子阵列中的各个单元也被连接到本地字线和本地位线。这个微型一电容一晶体管设计使其非常适合将大量存储单元封装到小面积中以实现高密度和高存储容量。而事实上,也有数十亿个 DRAM 单元可以被压缩到一个内存芯片上。

所以,和3D NAND Flash一样往高空发展的3D DRAM成为了目标。

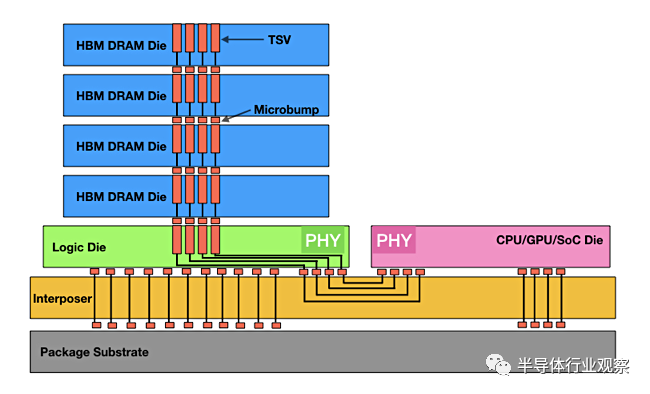

按照semiengineering在一篇报道中所说,通往 3D 的DRAM有两条道路,其中最直接的方法是保留当前的DRAM 技术并将多个芯片堆叠在彼此之上。这是用于高带宽存储器(HBM)的高级封装方法。常见的 HBM 芯片为 4 和 8 高,预计很快会达到 16 高。与基本 DRAM 相比,这是一种更昂贵的方法,因为在封装中堆叠die需要付出努力,但对于需要大量附近内存的应用程序(如人工智能),这是值得的。

但是,如果将其翻转到一边并旋转 90 度,则可以使用每层位线的阶梯设计对单元进行分层。这样,在 DRAM 制造过程中用于制作层的光刻图案化工艺可用于所有层——所谓的共享图案化——进而简化了制造工艺。

但毫无疑问,这都是他们前进的方向。

按照Yole的介绍,三星电子已经开始开发一种用于堆叠cell的技术,一种与高带宽存储器 (HBM) 大不相同的堆叠概念。此外,三星电子也在考虑增加DRAM晶体管的栅极(current gate)和沟道(current path)之间的接触面。这意味着三侧接触FinFet技术和四侧接触环栅(GAA)技术可以用于DRAM生产。当栅极和沟道之间的接触面增加时,晶体管可以更精确地控制电流。

在2022年9月接受日本eetimes采访的时候,美光公司也确认正在探索3D DARM的方案。

美光表示,3D DRAM 正在被讨论作为继续扩展 DRAM 的下一步。为了实现 3D DRAM,整个行业都在积极研究,从制造设备的开发、先进的 ALD(原子层沉积)、选择性气相沉积、选择性蚀刻,再到架构的讨论。

美光同时强调,3D DRAM目前碰到的主要问题仍然存在于成本和技术方面。技术挑战存在于广泛的领域,包括设备和结构、制造工艺、制造设备、材料和架构。“为了从平面DRAM转向3D DRAM,需要所有领域的创新。此外,这种转变需要在成本曲线和性能与 DRAM 缩放路线图相交的地方实现。”美光方面强调。

为此美光坦言,该行业继续扩展平面并寻找推进 DRAM 路线图的方法。此外,新的内存架构的开发也在进行中,因此DRAM在系统中的角色正在发生变化,或许有可能在更长时间内维持平面型。“在这一点上,内存制造商正在投资(平面和 3D)以预期拐点以保持 DRAM 的持续扩展,虽然DRAM的每个节点扩展变得越来越困难,但至少在接下来的几年里,传统的扩展将继续下去。”美光方面接着说。

Yole则表示,美光提交了与三星电子不同的 3D DRAM 专利申请。美光的方法是在不放置cell的情况下改变晶体管和电容器的形状。

至于SK海力士的3D DRAM方案,网上并没有看到太多介绍。不过Yole强调,SK海力士正在大力投入其中。除此以外,Applied Materials 和 Lam Research 等全球半导体设备制造商也开始开发与 3D DRAM 相关的解决方案。

具体到三大存储巨头在3D DRAM的表示,据businesskorea引述TechInsights 的数据显示,美光自2019年就已经开始了3D DRAM的研究,获得的专利数量是这两家韩国芯片制造商的两到三倍。

TechInsights进一步指出,在内存半导体市场排名第三的美光正积极准备蓝海市场,截止2022 年 8 月将获得 30 多项 3D DRAM 专利技术。相比之下,三星的3D DRAM专利不到 15 项 ,而SK 海力士持有的大约 10 项专利。

此外,国内多家研究机构甚至企业都在投入到3D DRAM的研发当中。中科院微电子所就曾经撰文表示,针对平面结构IGZO-DRAM的密度问题,微电子所微电子重点实验室刘明院士团队在垂直环形沟道结构(Channel-All-Around, CAA)IGZO FET的基础上,研究了第二层器件堆叠前层间介质层工艺的影响,验证了CAA IGZO FET在2T0C DARM应用中的可靠性。

另一个分析机构Techinsights则表示,如果现在的DRAM厂商还保持1T 1C结构的6F2 DRAMcell设计,到2027年或2028年亮相的10nm D/R将是最后一代的DRAM新技术。届时的DRAM单元缩放将面临诸如3D DRAM、row hammer scaling (circuit)、低功耗设计等挑战 、刷新时间缩放( refresh time scaling)和管理、低延迟、新work-function材料、HKMG 晶体管和片上 ECC等工艺技术的挑战。

imec则指出,包括电阻式 RAM、磁存储器(类似 MRAM)、相变存储器 (PCM) 和铁电存储器在内的新兴存储器已被研究用于替代经典存储器和存储解决方案(静态 RAM (SRAM)、DRAM 和 NAND-Flash),或填补传统计算机层次结构中快速且昂贵的 DRAM 与缓慢且廉价的 NAND 之间的空白(所谓的存储类内存)。

“然而,大多数新兴存储器都难以在市场上得到采用。这导致内存公司重新关注扩展动态内存的 DRAM 和存储的 NAND 闪存——以满足传统的密度需求。”imec说。

也就是说,对于DRAM厂商来说,探索如何提升密度,会是他们很长一段时间需要努力的方向。

来源:半导体行业观察