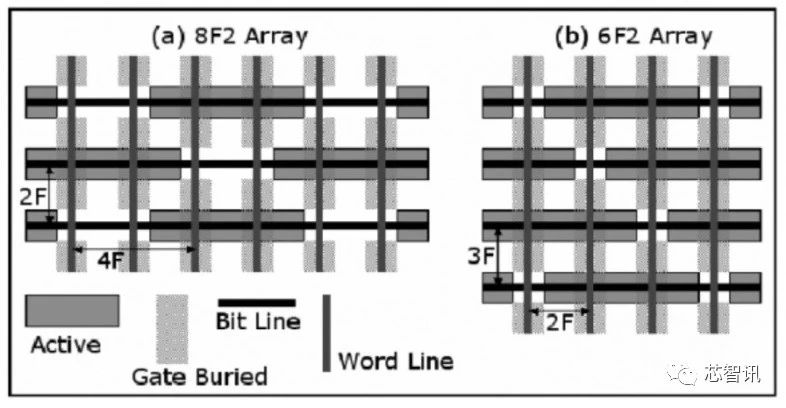

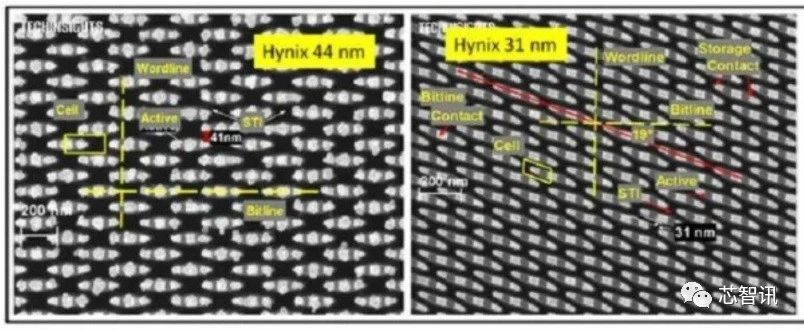

5月26日消息,据韩国媒体The Elec报道,存储芯片大厂三星组建了一支专业团队,负责开发 4F² DRAM 储存单元结构。相较现有 6F² DRAM 储存单元结构,在不改变制程下,4F² DRAM 储存单元结构芯片面积最高可减少达 30%。

报导指出,原本的 4F Square 是一种单元结构技术,DRAM 产业早在 10 年前就尝试进行商业化的动作,但最后以失败告终。

如今,三星再组建了专业的团队,研发 4F² DRAM 储存单元结构芯片,其新结构的晶体管将根据电流流入和流出的方向,形成源极(S)、栅极(G)和漏极(D)等整套系统。

其设备结构就是在漏极(D)上方安装一个储存电荷的电容器,晶体管和排列的 WL 线和垂直排列的 BL 线接触。其中 WL 连接到栅极(G),负责电晶体的开与关。而 BL 连接到源极(S),则是负责读取和写入数据。

编辑:芯智讯-林子

0