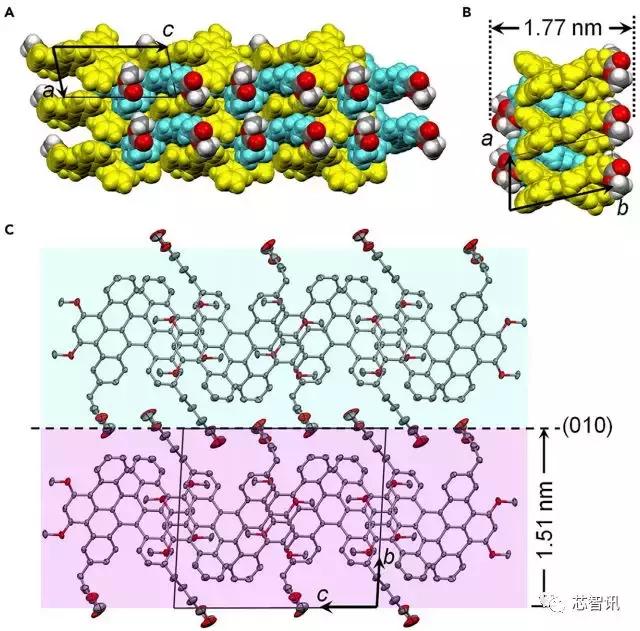

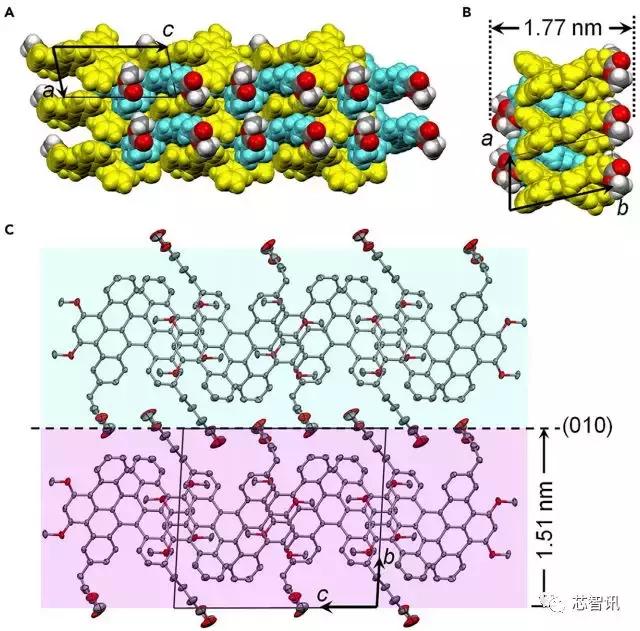

近日,台大携手台积电、美国麻省理工学院(MIT),研究发现二维材料结合半金属铋(Bi)能达到极低的电阻,接近量子极限,有助于实现半导体1nm以下的艰巨挑战;且这项研究已于“自然”(Nature)杂志公开发表。

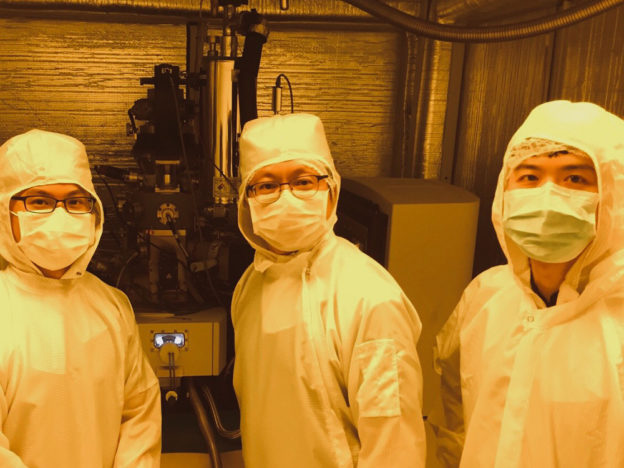

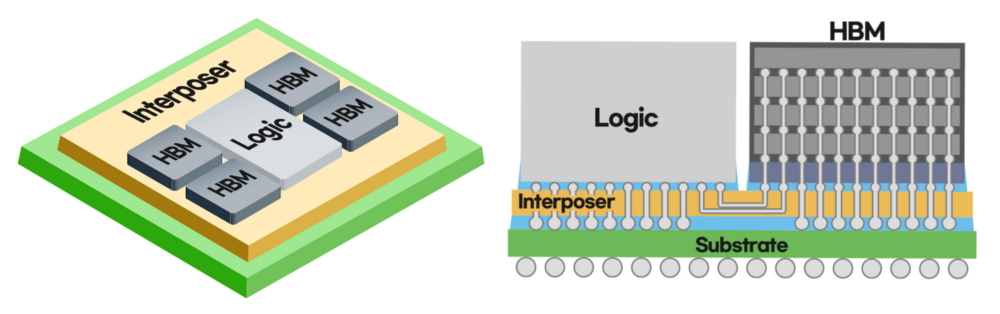

5月6月,三星对外宣布,基于其下一代2.5D 封装技术Interposer-Cube4 (I-Cube4) 的芯片即将上市。

摩尔定律在晶圆工艺制程方面已是强弩之末,此时先进的封装技术拿起了接力棒。扇出型晶圆级封装(FOWLP)等先进技术可以提高器件密度、提升性能,并突破芯片I/O数量的限制。然而,要成功利用这类技术,在芯片设计之初就要开始考虑其封装。

如果摩尔定律的尽头是一堵墙,第一个撞墙的人,就是跑在最前面的那个。

2019年11月7日,由ASPENCORE主办的全球CEO峰会在深圳喜来登大酒店召开。新思科技联席CEO Aart de Geus博士做了题为《后摩尔时代,Shift left抢占经济先机》的演讲,分享了其对于半导体行业的观察。

2019年9月4日,英特尔在北京召开了“英特尔先进封装技术解析会”,芯智讯也受邀参与了此次活动,得以对英特尔先进的多芯片封装架构,以及全新的封装技术一窥究竟。

“毋庸置疑,摩尔定律依然有效且状况良好,它没有死掉、没有减缓、也没有带病。”在第 31 届 Hotchips 国际大会上,台积电研发负责人、技术研究副总经理黄汉森(Philip Wong)博士在其专题报告中说道。他甚至在自己的 PPT 中提及,到 2050 年,晶体管的特征尺寸将到达 0.1nm。

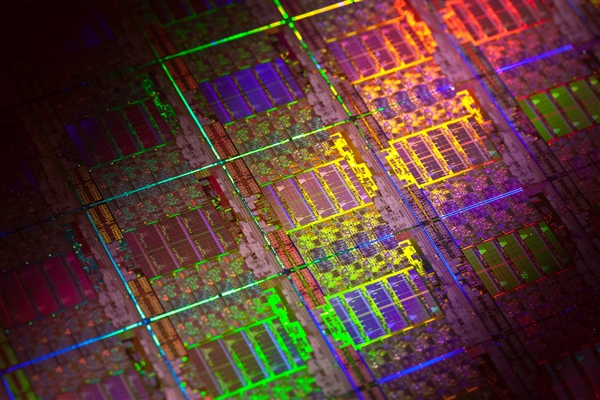

在半导体领域,“摩尔定律”可谓是无人不知、无人不晓。可以说在过去几十年,半导体产业在摩尔定律的推动下高速发展。但是现在,随着晶体管缩放尺寸逐渐逼近物理极限,半导体工艺制程的推进也越来越困难,“摩尔定律”已死的声音也开始不绝于耳。不过,即便如此,科学界也依然希望通过一些新的技术来继续推动摩尔定律的前进。

5月5日,紫光展锐首席执行官楚庆受邀参加第一财经《头脑风暴》,针对中国芯片业在企业管理、人才培养、产业投资、市场竞争上面临的机遇与挑战,分享了其极具战略性的观点及见解。

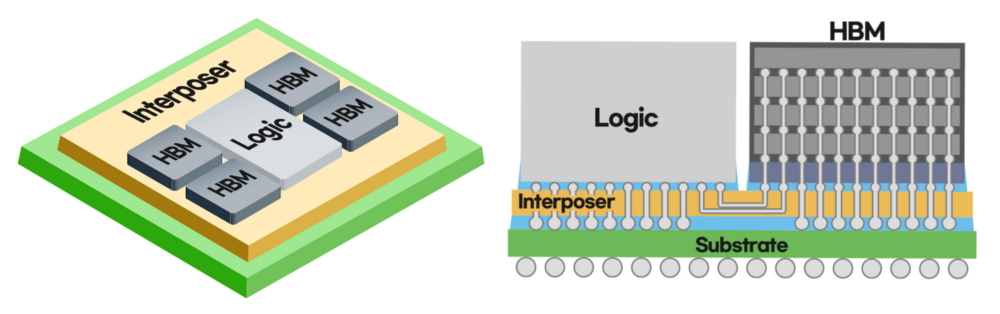

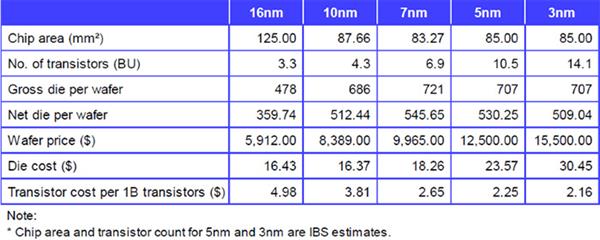

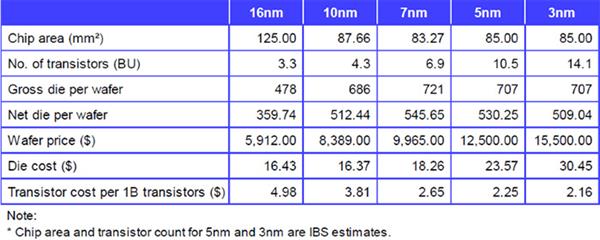

即便是进入到5nm、3nm工艺,制程提升带来的性能进步越来越小,台积电、三星公布的5nm工艺晶体管性能提升只有15-20%左右的水平,而摩尔定律的失效引发的问题不只是性能提升不尽如人意,还有成本的大幅上涨,这个问题可能比性能提升更麻烦。

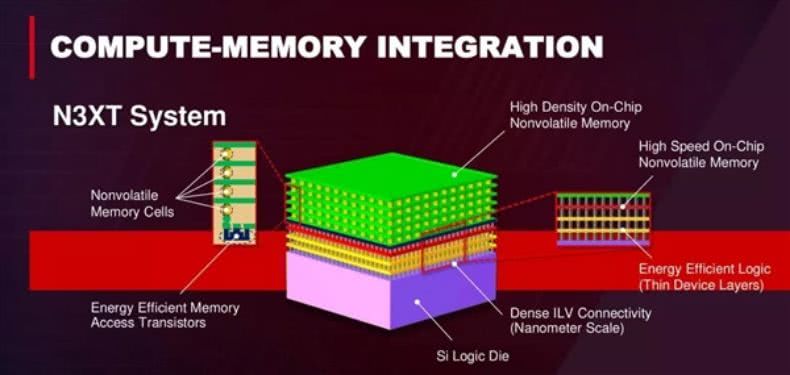

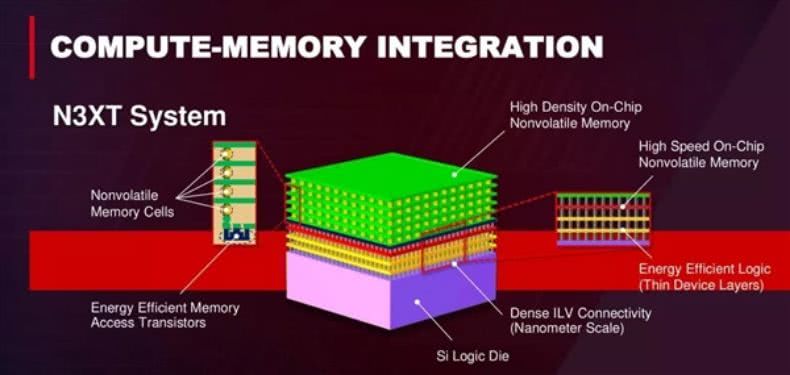

2018年的英特尔度过了它50岁的生日,同时也在这一年给吃瓜群众造了不少料。不过这也没什么好唏嘘的,毕竟没有任何一家企业能够运气好到在不断创造佳绩的同时,一帆风顺,没有一点挫折。今天我们重点来看看,这家50年来一直引领科全球科技的企业,如何在当今更为激烈的竞争环境中保持创新势头。下面芯智讯就从芯片制程工艺、异构及3D封装技术、人工智能、5G、前沿技术研究等多个维度来解析英特尔目前的现状:

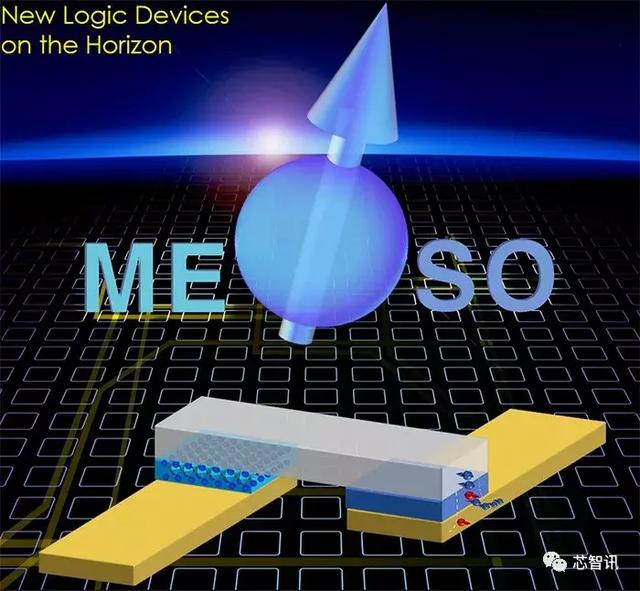

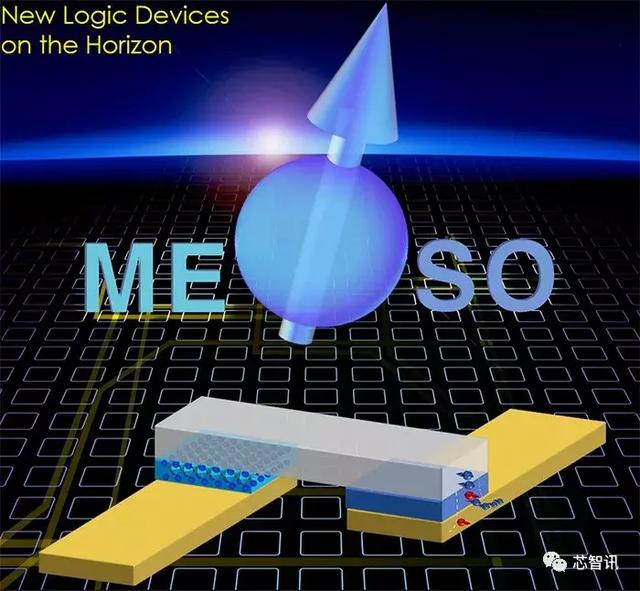

据外媒报道,英特尔近日已在“自旋电子学”的技术领域取得新进展。当地时间本周一,英特尔和加州大学伯克利分校的研究人员在《自然》杂志上发表的一篇论文中,公布了他们的自旋电子学研究进展。该论文的第一作者是英特尔组件研究小组的项目负责人Sasikanth Manipatruni。