“毋庸置疑,摩尔定律依然有效且状况良好,它没有死掉、没有减缓、也没有带病。”在第 31 届 Hotchips 国际大会上,台积电研发负责人、技术研究副总经理黄汉森(Philip Wong)博士在其专题报告中说道。他甚至在自己的 PPT 中提及,到 2050 年,晶体管的特征尺寸将到达 0.1nm。

Hotchips 国际大会是每年国际半导体芯片四大国际会议之一,大会主要聚焦于芯片架构、半导体制程以及芯片设计相关的技术。在第 31 届会议上,AMD、Intel、NVIDIA、IBM、台积电、三星、ARM等公司都在公布了他们的最新进展,展示的都是当前最新技术及未来的发展计划。但黄汉森的报告无疑是其中最抓人眼球的。

(来源:anandtech)

黄汉森的惊人发言,不禁让我们想起就在20年前,微电子学家胡正明教授拿着自己制作出来的第一款 45 纳米的 FinFET 晶体管,向工业界证明 200nm 以下是能够存在半导体晶体管的那一幕。

胡正明团队的 45 纳米 FinFET 器件性能优良,甚至打破了大多数人认为 35 纳米将是“摩尔定律”尽头的迷思,并且他大胆预测该器件能将摩尔定律推广到 20 纳米以下。而他的预言也在十几年后得到了验证,2011年 Intel 推出了首批商用的 FinFet 处理器。

说起半导体,我们不得不提到“摩尔定律”,这是一个神奇的定律,令无数人追赶,由 Intel 创始人之一戈登·摩尔(Gordon Moore)于 1965 年提出。其主要内容是,在单位面积集成电路上的晶体管数量会以两年为周期翻一倍。此定律一经提出,立刻成为行业的标杆,也是如今所有半导体人加班加点的原因,大家都为了这个目标而努力。

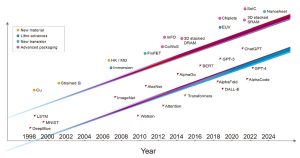

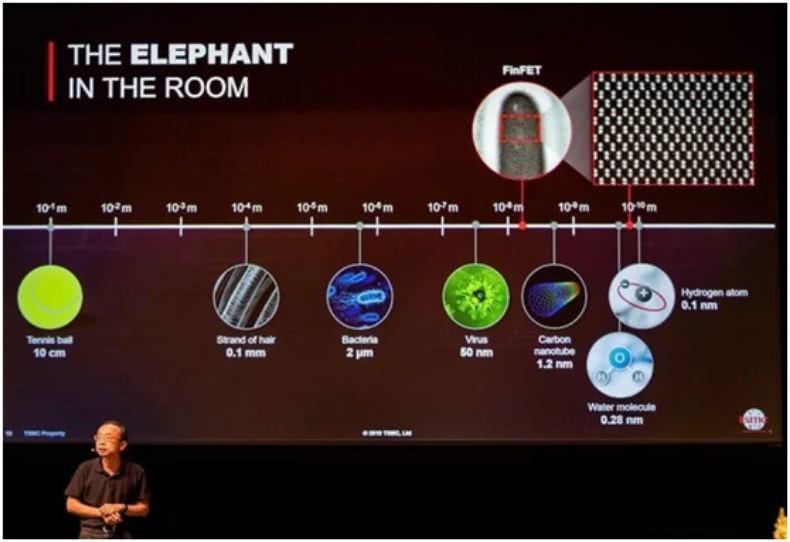

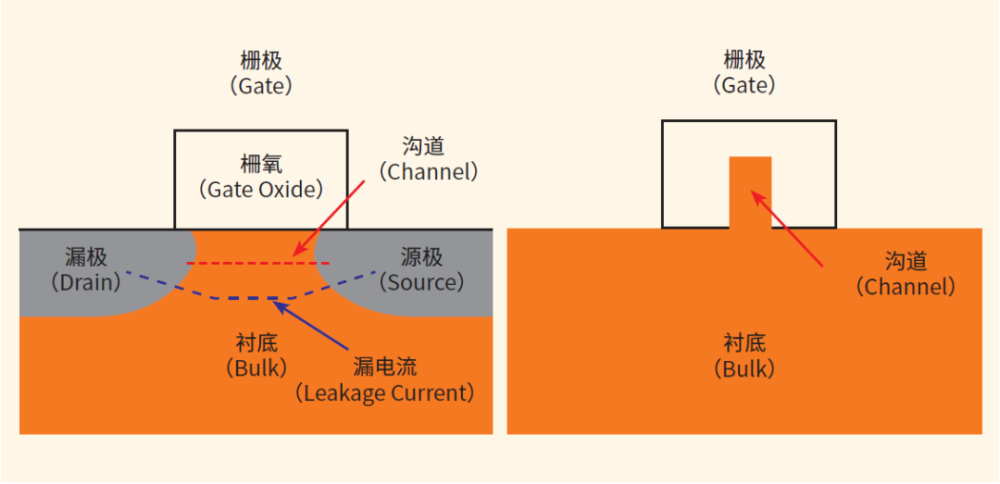

对此,黄汉森解读道,摩尔定律的关键在于芯片上晶体管的密度,要想放入更多的晶体管,而这也正是提高芯片性能的关键。在集成电路上挤入更多的晶体管,最直观的办法就是缩小晶体管的尺寸,例如提出新器件的结构设计,经典案例就是胡正明成功研制出的 FinFet,它将半导体器件结构的维度从二维提升到了三维,提升了我们对晶体管通断性质的控制,也很好地解决了由于尺寸缩小而带来的漏电流过大的问题。由此,我们的晶体管制程得以从 2002 年的 200 纳米工艺进化到到如今的 7 纳米工艺,大家似乎都没有失约。

新材料的出现也能够帮助我们缩小晶体管的尺寸,例如前几年很火的二维材料,例如石墨烯、还有以二硫化钼为代表的二维 TWD 材料等。它们都有着轻薄的特性,更为重要的是存在于它们中的电子迁移率高,简单说就是电子在它们中跑得很快。对此,黄汉森博士指出,二维材料的种类繁多,特性不一,好的材料我们可以慢慢选,大概有 2000 多种,未来的研究方向就像寻找钨灯丝一样。

图丨传统晶体管以及 FinFet 结构对比示意图(来源:anandtech)

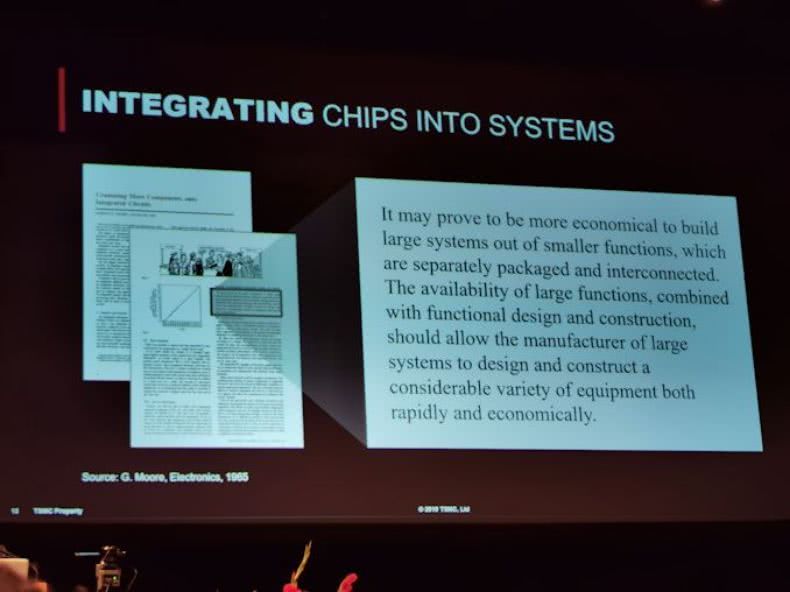

除了缩小尺寸,如果能充分利用芯片上的空间,也可以将更多的晶体管挤进芯片。换句话说,优化芯片架构是另一条路。对此,黄汉森搬出了 Moore 定律的原版论文,其中提出了一个观点——拥有复杂功能的芯片集成。而这个就是当下芯片架构研究和发展的方向,AMD 公司提出的 Chiplets 架构和台积电提出的“CoWoS” 晶圆级封装系统集成都是沿着这个方向发展的产物。

(来源:anandtech)

最近传出消息的有着 1.2 万亿晶体管的世界最大 AI 芯片以及华为新发布的华为达芬奇架构“NPU”,它们的架构与之相当类似。

简单而言,就是将一个或者多个芯片连同必须的存储器一起,放在一个芯片晶圆中制作出来,如此一来,芯片间以及芯片与存储之间的互联就变得更加紧密,一整块芯片系统的集成度自然就高了。更重要的是,这样的系统功能更加复杂,而且计算下来实现每一个功能的成本(Cost per function)降低。

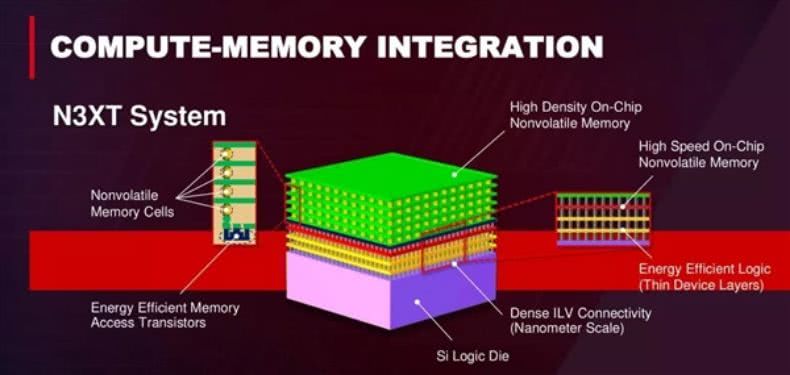

(来源:anandtech)

黄汉森认为,这将是未来芯片技术发展的趋势之一,任何能够优化芯片架构和芯片封装的技术都将快速发展,例如能将不同功能的芯片堆叠起来集成在一起的 3D 封装技术。

这又是一项将半导体芯片从二维层面拓展到三维的技术,就好像我们现在所说的第四代住宅,每层都有公共院落,每户都有私家庭院,可种花种菜、遛狗养鸟,可将车开到空中家门口,建筑外墙长满植物。一栋住宅就是一个小系统,它将之前分散建立在平地上的众多建筑物集成,形成有复杂功能的新型建筑。

说回“0.1nm”,这仅仅是黄汉森专题演讲 PPT 中的一张,而他并未明确指出到 2050 年,半导体制程会延续到 0.1nm。

毕竟,黄汉森是搞研发也是搞工程的人,说话做事还是有根据的,他通过介绍台积电最新的芯片技术,试图证明摩尔定律将继续延续下去。如今,7nm 的 FinFet 商用芯片早已面世,即将发布的华为麒麟 990 也被爆出采用的是最新的 7nm 工艺。黄汉森十分自信地表示,5nm 也在紧锣密鼓的研发中,已经投入试生产,而 3nm 则是台积电的下一个目标。

这不禁让我们想起 20 年前的胡正明,他预言 FinFet 技术能够将晶体管尺寸缩小至 20nm 以下,结果一语成谶。在其背后,我们看到的是人们追逐科技进步的力量。

-End-

参考:

https://www.anandtech.com/show/14770/hot-chips-31-keynote-day-2-dr-phillip-wong-vp-research-at-tsmc-145pm-pt

来源:deeptech