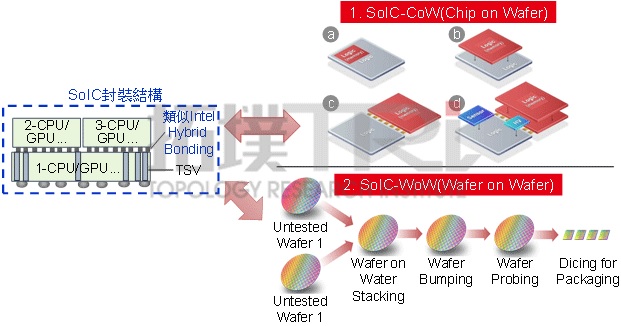

4月17日消息,据外媒naver报道,苹果公司正在台积电小量试产最新3D小芯片堆叠技术SoIC(系统整合芯片),最快有望2025~2026年有机会看到终端产品问世。

2月1日消息,晶圆代工大厂联电与EDA大厂Cadence于今日共同宣布,以Cadence Integrity 3D-IC 平台为核心的3D-IC 参考流程,已通过联电晶片堆叠技术认证,助力产业加快上市时间。

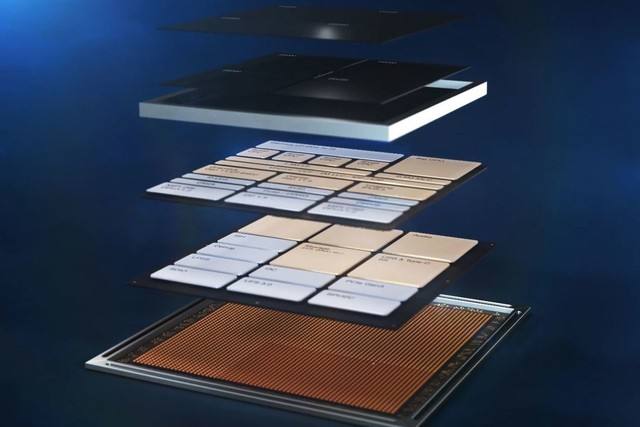

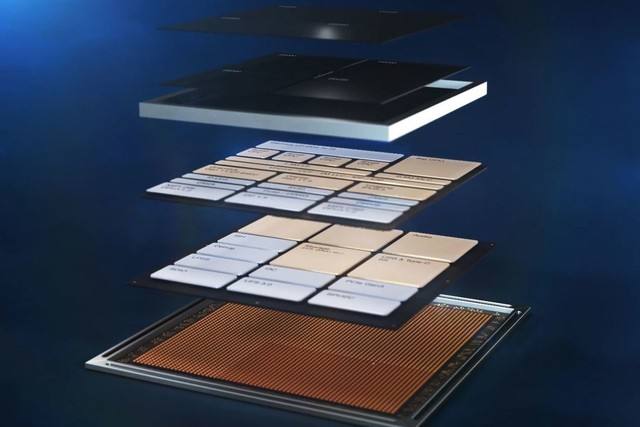

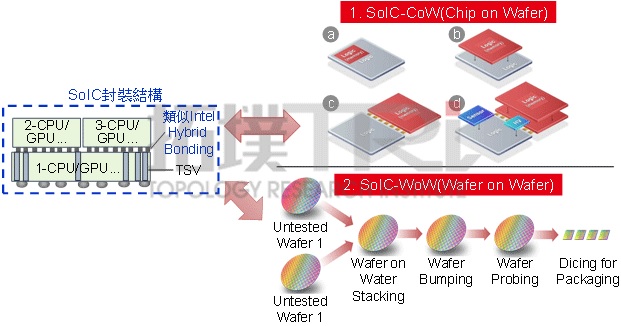

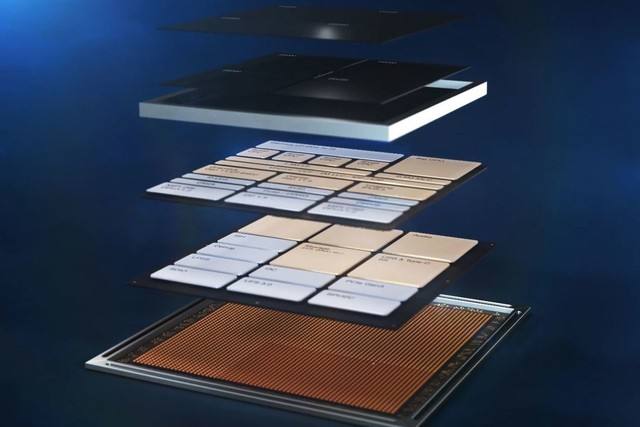

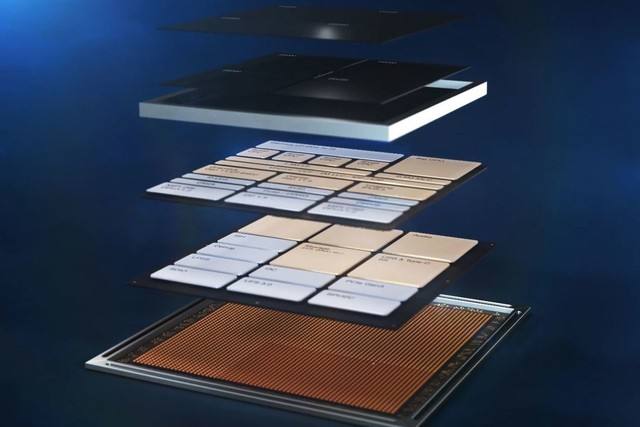

过去10 年全球数据运算量的发展已超越过去40 年的总和,随着各类应用对于算力要求的越来越高,摩尔定律的放缓,通过晶体管微缩所能够带来的性能提升也开始越来越有限,同时成本却在急剧上升。在此背景之下,业界开始采用2.5D/3D 立体堆叠的“异质整合(HIDAS)”封装、以及藉由硅中介层(Silicon Interposer)互连的“小芯片(Chiplet)”模组化架构来继续推动“摩尔定律”。

虽然在半导体先进制程工艺方面,近日三星成功抢先台积电量产了3nm GAA制程工艺,但是在2.5/3D先进封装技术方面,三星仍落后于英特尔和台积电。而为了缩短这方面的差距,三星也已经组建了新的半导体封装工作组发力先进封装技术。

6月24日消息,台积电今天宣布,子公司台积电日本3D IC研发中心,位于日本产业技术综合研究所的筑波中心完成无尘室工程,并在今天举行开幕仪式

10 月 8 日,中段硅片制造和三维多芯片集成加工企业盛合晶微半导体有限公司(SJ Semiconductor Co.)宣布,与系列投资人签署了总额为 3 亿美元的 C 轮增资协议,并已实现美元出资到位。参与增资的投资人包括光控华登、建信股权、建信信托、国方资本、碧桂园创投、华泰国际、金浦国调等,既有投资人元禾厚望、中金资本、元禾璞华也参与了本次增资。增资完成后,公司的总融资额将达到 6.3 亿美元,投后估值超过 10 亿美元。

中国上海,2021年10月8日——楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日正式交付全新CadenceÒ IntegrityÔ 3D-IC平台,这是业界首款完整的高容量3D-IC平台,将设计规划、物理实现和系统分析统一集成于单个管理界面中。Integrity 3D-IC平台支持了Cadence第三代3D-IC解决方案,客户可以利用平台集成的热、功耗和静态时序分析功能,优化受系统驱动的小芯片(Chilet)的功耗、性能和面积目标(PPA)。

随著 5G、IoT 与 AI 智慧时代持续引领终端应用,驱使 HPC 芯片逐步成为高阶产业于资料中心、深度学习与挖矿需求等领域训练与推论的重要发展关键。为求实现相关需求,高阶 2.5D / 3D IC 封装技术已是其中最佳解方,然而近年由于产品功能性和记忆体需求大增,间接影响相关封测技术发展,各主流大厂纷纷看到芯片与芯片间、逻辑芯片与存储芯片间信号沟通的重要性,对此提出相应的高阶 HPC 芯片封装主架构外,也尝试进一步运用小芯片 Chiplet 方式同步解决芯片间堆叠疑虑,期望改善信号传输效率和运算表现。

台湾半导体研究中心(TSRI)与日本产业技术总合研究所(AIST)合作,开发新型电晶体结构。日本媒体指出,这有助制造2nm以下线宽、规划应用在2024 年后的新一代先进半导体。