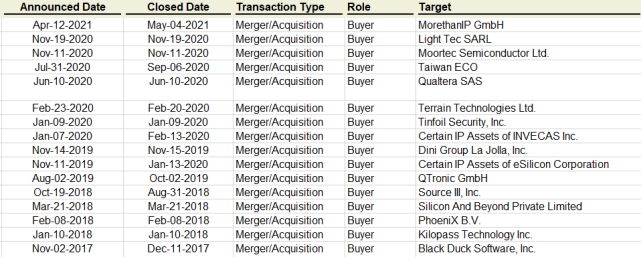

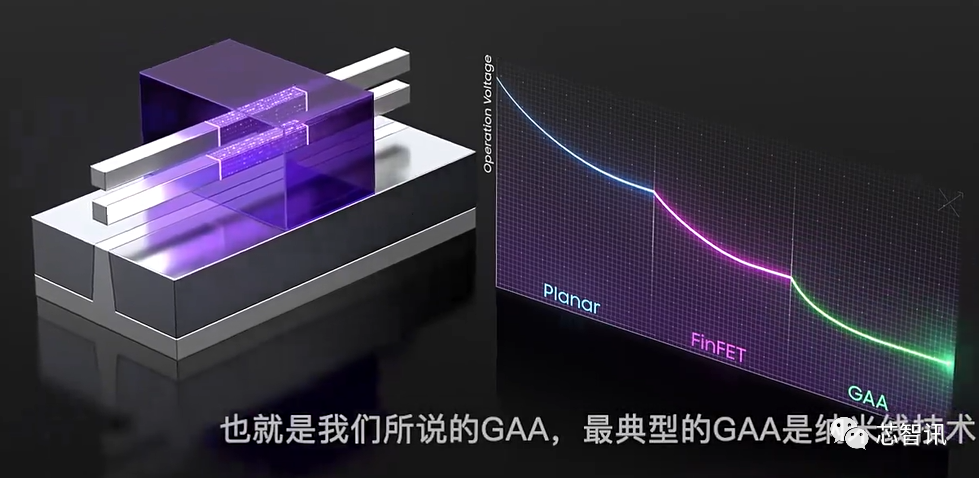

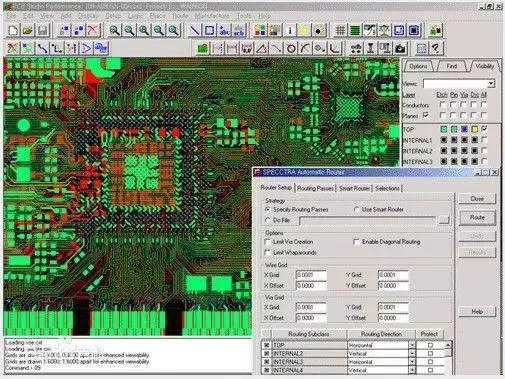

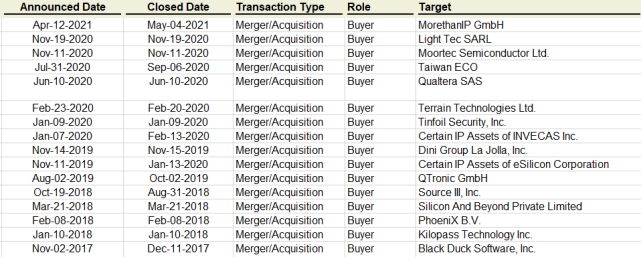

9月5日消息,随着美国对华限制可用于GAAFET的EDA 设计工具,凸显EDA 在芯片设计关键角色。由于目前EDA 产业高度集中,前三大厂商以美商为主。预计台积电2nm制程也将采用美商针对GAAFET 架构的EDA软件。另据台媒报道,包括联发科、鸿海旗下工业富联等,也积极布局EDA 工具。

放眼世界,我们面对的是百年未有之大变局,而半导体行业又挺立在大变局的潮头,成为大国竞争力的焦点。

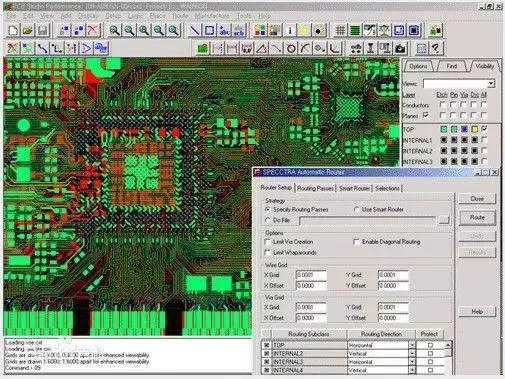

芯片设计既是一门艺术,也是一项极为复杂的工程,并且设计的风险和研发成本也越来越高昂。

8月3日消息,据外媒Protocol报道,美国准备对用于设计半导体的特定类型EDA软件实施新的出口限制。据悉,该软件是设计和制造最先进的人工智能芯片至关重要的下一代技术。

中国上海,2022年6月23日——楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布,其面向 TSMC N7、N6 和 N5 工艺技术 PCI Express®(PCIe®)5.0 规范的 PHY 和控制器 IP 在 4 月举行的业界首次 PCIe 5.0 规范合规认证活动中通过了 PCI-SIG® 的认证测试。Cadence® 解决方案经过充分测试,符合 PCIe 5.0 技术的 32GT/s 全速要求。该合规计划为设计者提供测试程序,用以评估系统级芯片(SoC)设计的 PCIe 5.0 接口是否会按预期运行。

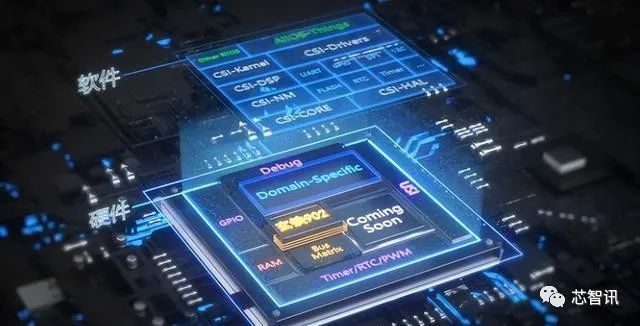

根据世界半导体贸易协会(WSTS)统计的数据,继2020年芯片设计IP销售额同比增长16%之后,2021年设计IP销售额同比增长了19.4%,达到54.5亿美元。与此同时,2021年半导体销售额同比增长了26.2%。基于此,IPnest于2022年5月发布了《设计IP报告》,按各类别对IP供应商进行了排名。

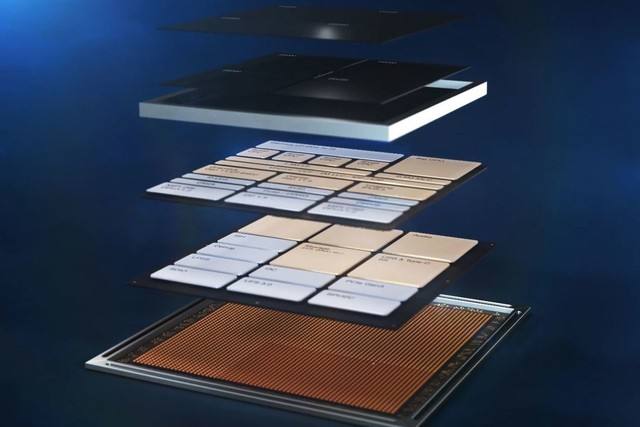

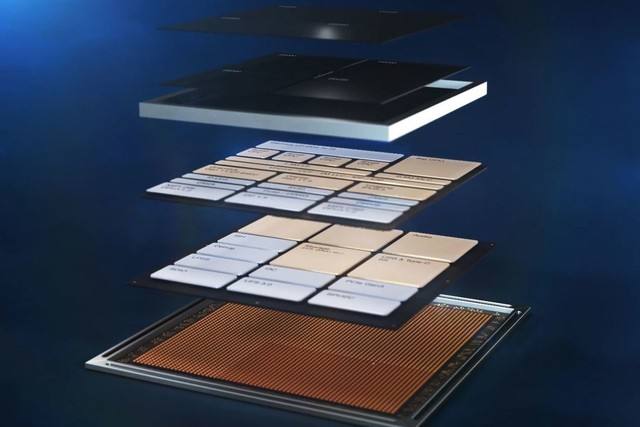

中国上海,2021年10月8日——楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日正式交付全新CadenceÒ IntegrityÔ 3D-IC平台,这是业界首款完整的高容量3D-IC平台,将设计规划、物理实现和系统分析统一集成于单个管理界面中。Integrity 3D-IC平台支持了Cadence第三代3D-IC解决方案,客户可以利用平台集成的热、功耗和静态时序分析功能,优化受系统驱动的小芯片(Chilet)的功耗、性能和面积目标(PPA)。

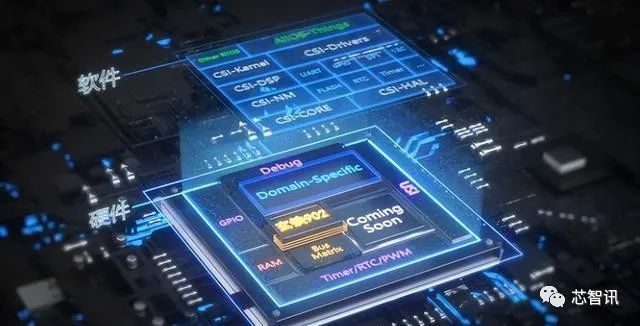

近年来,机器学习的快速发展使其在各行各业迎来了更加广泛和深入的应用,电子设计自动化领域也不例外。机器学习技术在该领域的应用已有二三十年的时间,期间相关技术的进展为电子设计自动化任务提供了更好的解决方案。全球三大 EDA 之一的 Cadence 推出了完全基于机器学习的芯片设计自动化工具 Cerebrus,实现了开发流程效率的提升,也得到了客户的认可。

6月21日晚间,深交所正式受理了国产EDA厂商——北京华大九天科技股份有限公司(简称“华大九天”)的创业板IPO申请。本次拟向社会公开发行股票 108,588,354 股,占发行后公司总股本的比例为 20%,拟募集25.51亿元,主要用于各类EDA工具的升级和开发等项目。

3月17日,楷登电子(美国 Cadence 公司,NASDAQ:CDNS)正式发布下一代Cadence Sigrity X信号和电源完整性(SI/PI)解决方案。Sigrity X搭载了全新的用于系统级分析的强大仿真引擎,并采用旗舰Cadence Clarity™ 3D Solver场求解器创新的大规模分布式架构。

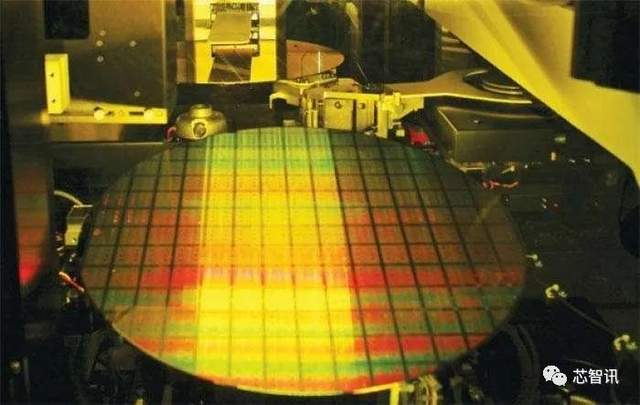

美国此次对华为芯片产业的全面限制升级,涵盖芯片设计的上游软件、芯片制造的上游设备以及当前最主要的有台积电代工生产的7nm的芯片制造。美国商务部对华为芯片产业链所有环节可谓是进行了一次定点式精准打击。首当其冲的的是芯片设计的上游EDA软件。虽然华为可以设计芯片,但是IC设计的高端软件EDA工具仍然基本上由Cadence、Synopsys、Mentor三家公司垄断。而在中国市场,这三家EDA软件公司更是占据了95%的市场份额。