3月20日,联发科宣布,推出新一代定制化芯片(ASIC)设计平台,提供异质整合电子与光学信号的传输界面的共封装光学(Co-Package Optics,CPO)解决方案。将于3月底在加州圣地亚哥举办的OFC大会上,展出与Ranovus合作的CPO解决方案,瞄准AI和高速运算市场。

据介绍,该前瞻设计平台采用联发科技自主研发的高速SerDes技术处理电子信号传输,并整合Ranovus公司领先业界的Odin光学引擎模块,实现高速电子与光学信号完美无缝接轨。透过共封装技术,将两者紧密结合在单一元件内,可提供高达8组800Gbps的频宽密集电子及光学信道,比目前主流解决方案更小面积、更低功耗且频宽密度最高。

更值得一提的是,该设计平台提供了弹性选配功能,可依不同应用场景灵活调整光电信道数量,最大程度满足客制化需求。此外,Odin®光学引擎模块还支持内置及外接式激光光源,可适用于更广泛的场景部署。

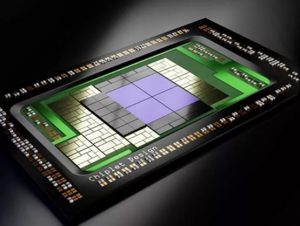

凭借联发科技领先的3nm制程、先进封装技术、芯片散热解决方案以及长期累积的光学设计经验,这款ASIC设计平台不仅具备顶级性能和密度,更提供从设计、制造到测试验证的完整服务。它涵盖了业界最先进的芯片对芯片高速互连技术、多样异质整合封装方式、高速PCIe/HBM內存界面等,足以满足未来AI、HPC、数据中心等严苛的应用需求。

联发科资深副总经理游人杰表示:“生成式AI的崛起,对內存频宽、容量以及高速I/O的需求大幅提升,光电芯片整合技术将成为未来关键。我们最新推出的异质CPO设计平台,结合公司在先进制程、散热和光学领域的长期积累,定能为客户提供最前瞻、最灵活的高速I/O解决方案。”

0