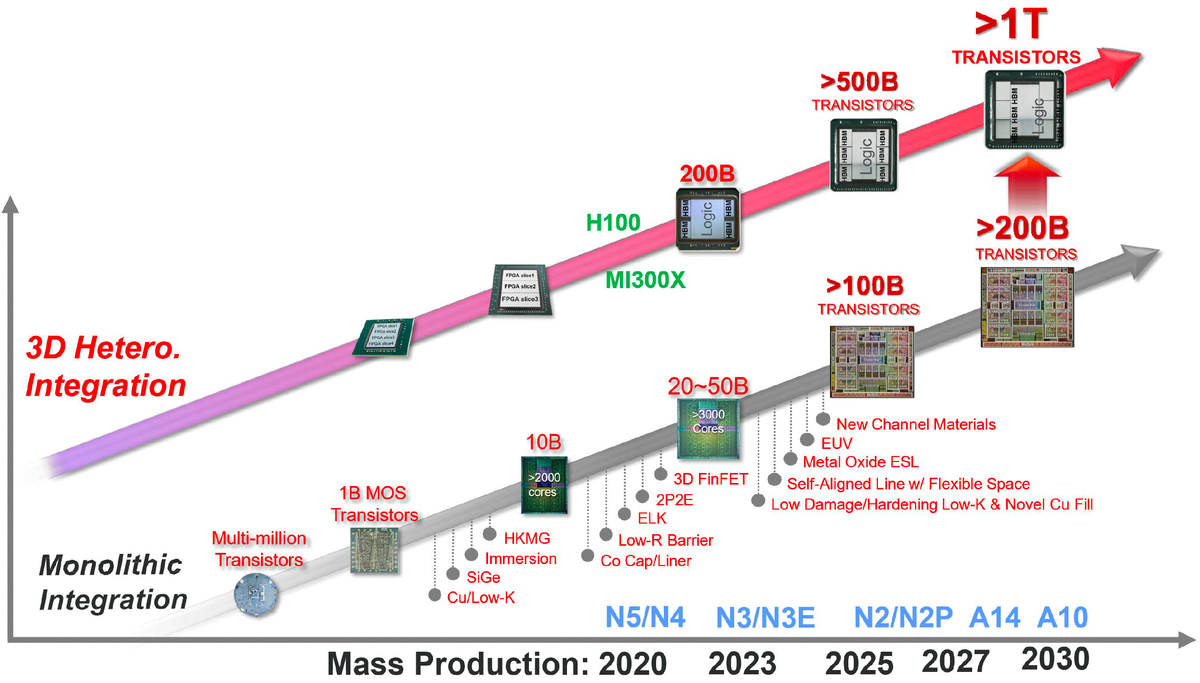

12月28日消息,据外媒tomshardware报道,晶圆代工大厂台积电在IEDM大会上分享了其最新的Roadmap,计划在2023年推出1nm级的A10制程,实现单个芯片上集成200亿个晶体管,并依托于先进封装技术,实现单个封装上集成1万亿个晶体管的目标。

具体来说,根据台积电的计划,首先会在2025年量产2nm级的N2制程,2026年左右量产N2P制程,届时将会采用新的通道材料、EUV、金属氧化物ESL、自对齐线w / Flexible Space、低损伤/硬化Low-K ?& 新型铜填充等技术,将实现单颗芯片集成超过1000亿个晶体管,同时借助先进的3D封装技术,实现单个封装集成超过5000个晶体管。

在2027年之后,台积电还将量产1.4nm级的A14制程,2030年将量产1nm级的A10制程,实现单芯片集成超过2000亿个晶体管,借助3D封装技术,实现单个封装内集成超过1万亿个晶体管。

虽然近年来,摩尔定律的推进持续放缓,但是台积电深信,随着2nm、1.4nm和1nm制程推出,未来五六年内,半导体芯片仍能在性能、功耗和晶体管密度进一步提升。

目前市场上最复杂的单片处理器之一就是英伟达(Nvidia)的GH100,拥有800亿个晶体管。台积电表示,不久将出现更复杂的单晶片,晶体管数量将超过1000亿个,但制程上会越来越复杂,成本也会变高,因此许多公司会选择多芯片封装设计,如AMD MI300X和英特尔Ponte Vecchio就由几十个芯片组成。

编辑:芯智讯-浪客剑

0