格芯(GLOBALFOUNDRIES)官方在今天凌晨正式宣布:为支持公司战略调整,格芯将搁置7纳米FinFET项目,并调整相应研发团队来支持强化的产品组合方案。在裁减相关人员的同时,一大部分顶尖技术人员将被部署到14/12纳米FinFET衍生产品和其他差异化产品的工作上。

这一消息来的太过突然,格芯官网上7nm FinFET的介绍都还没来得及撤下。2017年6月14日发布的一篇题为“格芯交付性能领先的7纳米FinFET技术在即”的新闻稿也赫然在列。

在那篇新闻稿中,格芯这样写道:

格芯今日宣布推出其具有7纳米领先性能的(7LP)FinFET半导体技术,其40%的跨越式性能提升将满足诸如高端移动处理器、云服务器和网络基础设施等应用的需求。设计套件现已就绪,基于7LP技术的第一批客户产品预计于2018年上半年推出,并将于2018年下半年实现量产。

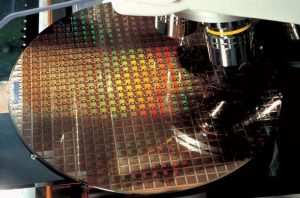

2016年9月,格芯曾宣布将充分利用其在高性能芯片制造中无可比拟的技术积淀,来研发自己7纳米FinFET技术的计划。由于晶体管和工艺水平的进一步改进,7LP技术的表现远优于最初的性能目标。与先前基于14纳米FinFET技术的产品相比,预计面积将缩小一半,同时处理性能提升超过40%。目前,在格芯位于纽约萨拉托加县的全球领先的Fab 8晶圆厂内,该技术已经做好了为客户设计提供服务的准备。

2017年10月,格芯首席技术官Gary Patton在上海举行的一次技术会议上还披露,7nm EUV极紫外光刻技术的良品率已经提高到65%,公司将按计划推进EUV的商用和普及。

然而……

7nm,想说爱你不容易

搁置7纳米FinFET项目,这被业界视作是今年初汤姆·嘉菲尔德(Tom Caulfield)接任首席执行官后,格芯在战略转型上迄今为止迈出的最重要,也是最为大胆的一步。

格芯方面给出的说法是,公司正在重塑其技术组合,重点关注为高增长市场中的客户提供真正的差异化产品。为此,格芯一是将相应优化开发资源,让14/12纳米FinFET平台为这些客户所用,提供包括射频、嵌入式存储器和低功耗等一系列创新IP及功能;二是继续侧重于FDX™平台、领先的射频产品(包括RF SOI和高性能锗硅)和模拟/混合信号,以满足越来越多低功耗、实时连接、车载设计需求的其他技术。

2017年2月10日,格芯宣布在中国成都高新西区建立12英寸代工厂,在半导体业界造成了巨大的影响:项目一期为成熟的130nm和180nm工艺,二期则为其22 FDX FD-SOI工艺,建成后年产能将达到100万片。

一方面,此举完成了全球Top 3代工厂在中国的布局;另一方面,更受关注的是FD-SOI工艺经过几年的酝酿,终于落户中国。

格芯中国区总经理白农评论道,“对我们中国的客户及生产合作伙伴而言这是一个积极的变化,因为我们强化了聚焦差异化的技术比如FDX (FD-SOI)及其他。这些差异化技术在中国市场的需求不断增加,对格芯而言一直相当重要。我们对FD/SOI以及与成都政府合作的承诺从未改变。”

“从本质上讲,每一代技术节点正在向为多个应用领域提供服务的设计平台过渡,从而为每个节点提供更长的使用寿命。这一行业动态导致设计范围到达摩尔定律外部界限的无晶圆厂客户越来越少。我们正重组我们的资源来转变业务重心,加倍投资整个产品组合中的差异化技术,有针对性的服务不断增长的细分市场中的客户。”嘉菲尔德对媒体表示。

如果这段表述听起来“过于官方”的话,那么Gartner研发副总裁Samuel Wang的解读则更为简单明了。

他分析认为,虽然最先进技术往往会占据大多数的热搜头条位置,但鲜少有客户能够承担为实现7纳米及更高精度所需的成本和代价。相比之下,14纳米及以上技术将在未来许多年继续成为芯片代工业务的重要需求及驱动因素。格芯的这一做法,真正减轻了前沿技术领域过重的投资负担,让格芯这样的企业能够对物联网、IoT、5G行业和汽车等快速增长市场中对大多数芯片设计人员真正重要的技术进行更有针对性的投资。

此外,为了更好地施展格芯在ASIC设计和IP方面的强大背景和重大投资,格芯还宣布了另一项重大举措:即建立独立于晶圆代工业务外的ASIC业务全资子公司。该独立ASIC实体将为客户提供7纳米及以下的晶圆代工替代选项,让ASIC业务部与更广泛的客户展开合作,特别是日益增多的系统公司,他们需要ASIC服务同时生产规模需求无法仅由格芯提供。

独立出来的ASIC设计服务公司,将不可避免的与市场上现有的其他设计服务公司展开竞争。但它同时也摆脱了限制,可以不再区分FinFET和FD-SOI工艺,不再纠结到底是选台积电还是SMIC,一切以客户需要为根本出发点。

ASIC设计服务,越来越刺激了!

不玩7nm的,不止格芯

就在一周前,联电(UMC)也宣布“不再投资 12 纳米以下的先进工艺!”

这个宣布在全球半导体产业引起轩然大波,外资分析师看法两极,摩根斯坦利分析师詹家鸿在七月报告中认为,联电是“把钱花在正确的地方”,上调联电的投资评等;UBS(瑞银集团)也给予买进评等;花旗证券则持续质疑联电在28纳米的竞争力,给予卖出评等。

“联电的客户群缩小,但先进工艺每个世代,产能的投资成本愈来愈高。”联电共同总经理王石此前在接受财经媒体采访时分析认为,如果把联电和台积电比喻成战舰。在先进工艺的战争中,联电这条战舰愈来愈小,台积电愈来愈大。过去18年,每当台积电这条大船换上口径更大的大炮,联电也努力要做同样的事,期待靠技术领先,扩大规模;但18年过去了,这件事却一直没有发生。

追赶策略让联电长期处于劣势。“一旦客户群变小,技术和资源就变少,你持续投入,但是推出的时间会比人家晚。”经常出现的状况是,联电赶上台积电最新工艺时,这项新工艺也过了价格最高的黄金时期,开始降价;同样投入先进工艺,联电就要花更多时间,才能把投资在研发和建置产能的钱收回来。

就以28纳米为例,这是当前晶圆代工产业最赚钱的服务,联电是少数紧追在台积电之后开发出28纳米工艺的公司;但只要联电一追上,台积电的28纳米就改版,“每次改版,客户就会改用新工艺,”联电只好再投资一次,台积电光是用这个方式,就已经“累死对手”。

“我们到了不能不改变的时候。”王石直言,一个最明显的指标是,由于过去的过度投资,联电必须要维持产能利用率高达9成以上,才能够赚钱,“我们的EPS(每股税后纯益)是用力拧毛巾挤出来的,”他认为,“以前我们是用牺牲获利,来换取营收成长。”

“但不继续追赶先进工艺,是不是对的决定?”为了回答这个问题,王石在公司内部已经追踪了好几年;他发现,破解台积电“累死对手”策略的关键,是用理性和纪律,扎实地建立联电在市场上的影响力和财务纪律。

台积电最新技术蓝图:7纳米量产,5纳米试产

来自EETimes美国的报道称,台积电(TSMC)在美国硅谷举行的年度技术研讨会上宣布其7纳米制程进入量产,并将有一个采用极紫外光微影(EUV)的版本于明年初量产。该公司也透露了5纳米节点的首个时间表,以及数种新的封装技术选项。

台积电继续将低功耗、低泄漏电流制程技术往更主流的22/12纳米节点推进,提供多种特殊制程以及一系列嵌入式内存选项;在此同时该公司也积极探索未来的晶体管结构与材料。整体看来,这家台湾晶圆代工龙头预计今年可生产1,200万片晶圆,研发与资本支出都有所增加;台积电也将于今年开始在中国南京的据点生产16纳米FinFET制程芯片。

唯一的坏消息是,台积电的新制程节点是不完全步骤,因此带来的优势也越来越薄;而新的常态是当性能增加,功耗下降幅度通常在10~20%左右,这使得新的封装技术与特殊制程重要性越来越高。

台积电已经开始量产的7纳米制程,预期今年将有50个以上的设计案投片(tap out),包括CPU、GPU、AI加速器芯片、加密货币采矿ASIC、网络芯片、游戏机芯片、5G芯片以及车用IC。该制程节点与两个世代前的16FF+制程相较,能提供35%的速度提升或节省65%耗电,闸极密度则能提升三倍。

将采用EUV微影的N7+节点,则能将闸极密度再提升20%、功耗再降10%,不过在速度上显然没有提升──而且这些进展需要使用新的标准单元(standard cells)。台积电已经将所谓的N7+节点基础IP进行硅验证,不过数个关键功能区块还得等到今年底或明年初才能准备就绪,包括28-112G serdes、嵌入式FPGA、HBM2与DDR 5界面。

台积电研究发展/设计暨技术平台副总经理侯永清(Cliff Hou)预期,该EUV制程在布局IP方面需要多花10%~20%的力气:“我们开发了一种实用方法以渐进方式来转移IP。”他表示,经过完整认证的N7+节点EDA流程将在8月份完成;在此同时,该节点的256Mbit测试SRAM良率已经与初期版本的7纳米节点相当。

展望未来,台积电预计在2019上半年展开5纳米制程风险试产,锁定手机与高性能运算芯片应用;相较于第一版不采用EUV的7纳米制程,5纳米节点的密度号称可达1.8倍,不过功耗预期只降低20%、速度约增加15%,采用极低阈值电压(Extremely Low Threshold Voltage, ELTV)技术则或许能提升25%;台积电并未提供ELTV技术的细节。

来源:国际电子商情