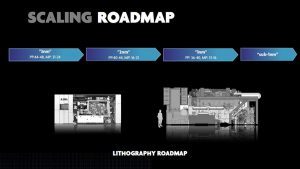

可以说在过去几十年,半导体产业在摩尔定律的推动下持续高速发展。但随着晶体管缩放尺寸逐渐逼近物理极限,半导体工艺制程的推进也越来越困难,“摩尔定律”已死的说法被越来越多的人认同。目前台积电、三星、英特尔等少数的尖端制程制造商,也只能依靠着越来越昂贵的EUV光刻机在艰难的推动半导体制程微缩,但是这依旧面临着非常多的工艺上的挑战以及成本难题。对此,科技界也希望寻找一些新的技术路径来改变目前的半导体制造困境,比如定向自组装(DSA)技术。

DSA技术再度兴起

严格来说,DSA技术并不是一项新技术。早在十年前,当半导体行业正在努力发展EUV光刻技术时,DSA技术几乎成为了每一家决心跨过193nm(光源)光刻机限制的制造商的前沿技术路线。这也是2012年SPIE高级光刻会议的热门话题,应用材料公司的一位与会者称DSA技术具有颠覆行业的潜力。

然而,与半导体行业的许多新技术一样,DSA解决重大行业挑战的潜力所带来的希望和兴奋很快就遇到了越来越难以克服的挑战。缺陷控制、可扩展性和集成到现有工作流程的复杂性阻碍了进展。随后,DSA被大多数公司搁置,尤其是随着EUV技术逐步被应用于生产。

但是DSA最初针对的问题,比如在当前光刻技术的限制下改进图案的CD特征值(光刻系统能够放大的最小精度,CD=k1*λ/NA)过程中,并没有消失。此外,一些新的缺陷,如最先进的EUV节点中的随机缺陷正在出现。Fractilia首席执行官Chris Mack表示,随机性可以占大批量制造商(HVM)EUV图案化错误预算总额的50%以上。[2]

imec的研发团队负责人Hyo Seon Suh表示:“对DSA的普遍批评是,由于结构的自组装性质,很难控制缺陷。”“但EUV中的随机缺陷也很难控制,这就是为什么许多行业和我们的核心芯片制造商合作伙伴再次将DSA视为纠正随机问题的可行选择。”

英特尔发言人还表示,该公司目前正在开发几种利用定向自组装(DSA)的集成工艺流程。“我们在SPIE等会议上公开讨论的一个工艺流程是使用DSA进行EUV抗蚀剂整流。DSA可以从根本上改善EUV光刻固有的系统性和随机性变化。使用这项技术,英特尔展示了一种DSA增强的EUV多图案化方法,最终金属间距为18nm,电气性能稳健。”

其他人也表示同意。布鲁尔科学公司首席技术官Rama Puligadda表示:“DSA正在回归。”“但形式完全不同。它被用来辅助EUV,主要是用来校正线条。”

定向自组装(DSA)通常被描述为共聚物材料自组装以在半导体衬底上形成纳米级分辨率图案的过程。虽然这是一个准确的描述,但它并没有提供太多细节来说明这一过程是如何完成的,以及为什么这些共聚物材料会以这种方式表现。对这一过程进行一些简化的解释有助于理解DSA技术如何有利于CD分辨率并为较低的制程工艺节点提供修复。

分离科学——从沙拉酱到半导体

DSA原理在大自然中随处可见,比如我们的脂质膜到细胞结构,再到DNA能够复制,并且一代代的遗传下去,就是一种自然组装技术。

天然的DSA形状是纳米级的,有规律和周期性,还很长,这就是我们在晶体管排列中所需要的,重要的是,它们能够提供比传统晶体管蚀刻更为精细的细节。[5]

以下内容可能不太容易理解,所以这里先借用美国研究人员Karl Skjonnemand关于自组装技术的TED演讲视频来便于大家理解:

正如油和醋由于其不相容的性质会分离成不同的层一样,DSA中使用的某些聚合物表现相似,在纳米尺度上。DSA通常将苯乙烯(S)单体结合形成聚苯乙烯(PS),并将甲基丙烯酸甲酯(MMA)单体组合形成聚甲基丙烯酸甲酯或PMMA。

DSA中通常使用的聚合物,如聚苯乙烯和PMMA,被设计成类似于油和醋的化学相分离。与后者不同,后者的分离是均匀的,在DSA中,这些聚合物的分离可以被仔细控制,从而产生精确的纳米级结构。

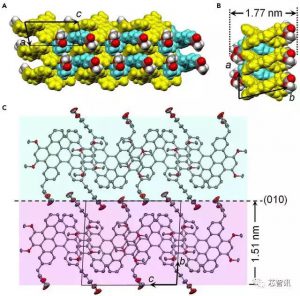

△图1:PS-b-PMMA嵌段共聚物的形态。资料来源:Semiconductor Engineering/Gregory Haley

PS通常通过阴离子聚合来合成。这包括使用像钠或钾这样的强碱来形成碳负离子,碳负离子在链的生长中起着至关重要的作用。阴离子聚合提供的精确控制使其成为生产具有特定长度和分子量的聚合物的理想选择。另一方面,PMMA可以通过自由基聚合或原子转移自由基聚合(ATRP)来合成。尽管与PS合成不同,但这两种工艺都致力于制造具有特定特性的聚合物。这是重要的,因为DSA过程中得到的结构的形状由这些聚合物的最终构型决定。[3]

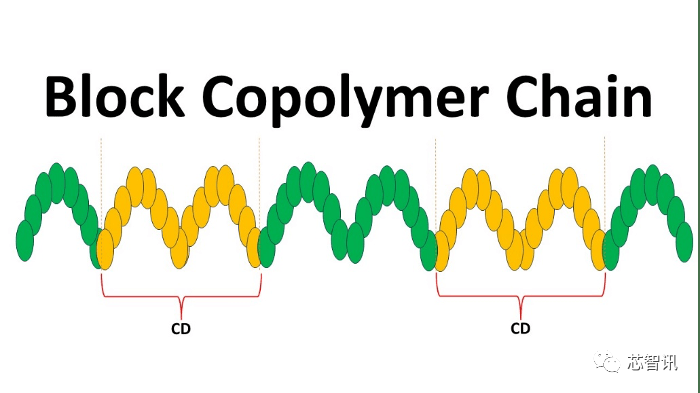

当使用诸如ATRP的技术合成时,PS和PMMA聚合物形成嵌段共聚物(BCP)PS-b-PMMA。PS和PMMA的嵌段在聚合物链内共价连接,但由于其化学差异,它们分离成不同的结构域(见图1)。

PS也是疏水性嵌段,其中PMMA是亲水性的,因此当它们形成链时,BCP的PS端连接,PMMA端连接,同时相互排斥。(图2)

△图2:PS-b-PMMA BCP链中产生的不同结构域为半导体结构提供了基础模板。资料来源:Semiconductor Engineering/Gregory Haley。

应该注意的是,嵌段之间的能量差越大,它们之间的偏析就越明显,这允许更小的链长度和对可以形成的CD的更精细的控制。[1]

然而,与半导体制造业的大多数事情一样,没有什么是免费的。如果能量差太大,可能会导致过度的相分离,从而可能导致加工复杂性或制造过程中的缺陷。平衡区块之间的能量差、链长度和所需的域大小需要仔细优化和考虑具体应用。实现这种平衡是一项复杂的任务,需要对聚合物化学进行精确的控制和理解。

定义CD

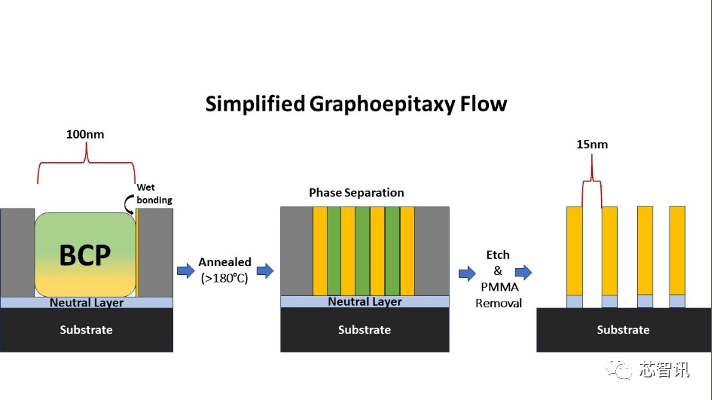

使用DSA对硅进行图案化有两种有效的方法——石墨外延流和化学外延流。石墨外延流使用传统光刻法对尺寸通常为最终CD尺寸的2倍至5倍的衬底进行构图。用BCP填充沟槽并退火(>180°C)以诱导相分离。沟槽的底部必须是中性的,以防止BCP粘附在基底上,同时一面墙与BCP湿结合。所得结构的CD由BCP链的长度定义(见图3)。

△图3:一个简化的流动演示了石墨定向自组装。资料来源:Semiconductor Engineering/Gregory Haley

△图3:一个简化的流动演示了石墨定向自组装。资料来源:Semiconductor Engineering/Gregory Haley

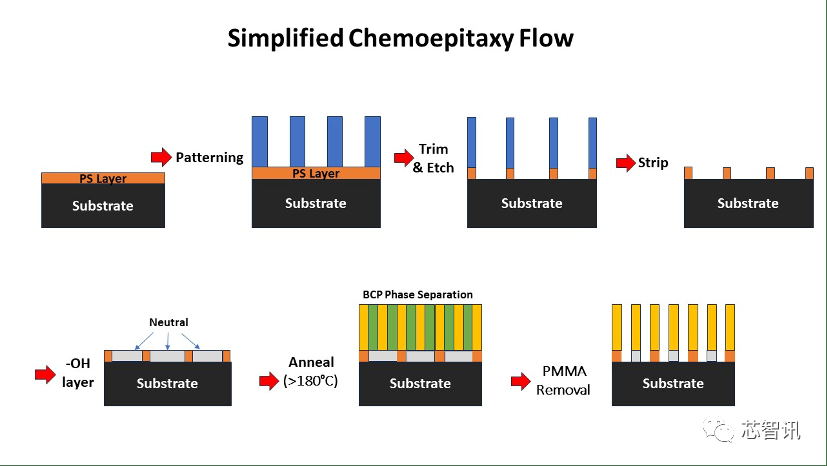

另一方面,化学外延流依赖于不同的表面能来排列BCP层。在这个过程中,交联PS的区域被施加到衬底上的中性区域旁边。BCP中的PS与交联的PS形成键,但与PMMA不形成键,并且中性区域不形成键。PS键为BCP流提供了锚,使相移的BCP在垂直维度上对齐(见图4)。

△图4:显示化学外延DSA的简化流程。资料来源:Semiconductor Engineering/Gregory Haley

“例如,如果你使用193nm光刻工艺,它就无法形成这种间距图案,”imec的研发团队负责人Hyo Seon Suh说。“但我们可以制作一个更大的间距模式,并用DSA填充。这被称为‘间距分割’。DSA使制造商可以实现只有EUV光刻机才能实现的尺寸,但无需购买EUV光刻机。”

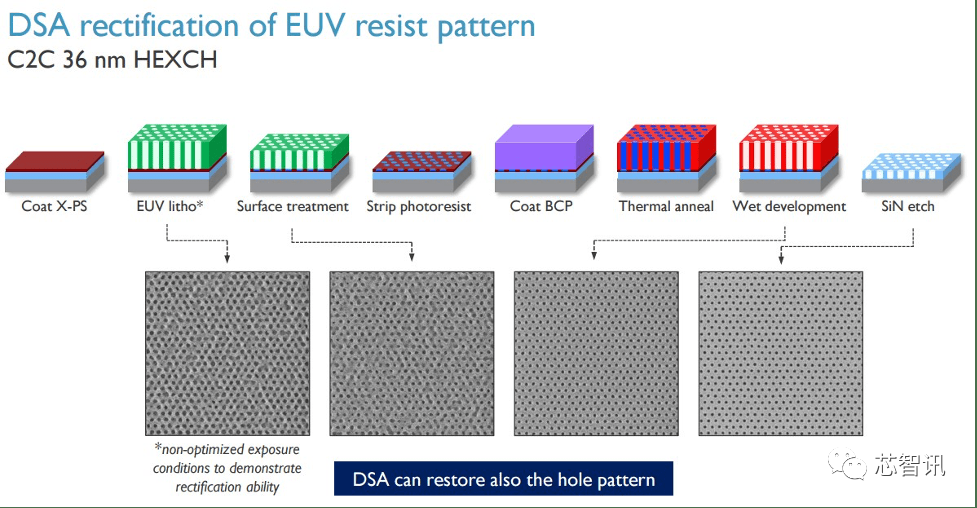

DSA的优点之一是其根据PS与PMMA的单体比例形成不同结构的灵活性。当每种聚合物的比例约为50%时,可以获得如上图所示的片状图案。一个块与另一个块的比率显著较低可以在较大块的矩阵内形成较小块的球体,而相同块的比率较高可以形成圆柱形结构。这有助于提高孔的CD,甚至使孔倍增(见图5)。

“定义结构不需要完美,”Hyo Seon Suh补充道。“我们只需要一些模式,我们可以引导局部聚合物的自组装,从而形成干净的模式。”

△图5:从较大的孔图案中获得较小尺寸孔图案的过程。来源:imec

如上所述,这些是两种一般类型的工艺流程的简化示例,尽管每种工艺流程中都有多个子集,使用不同的化学品、材料和层;行动命令;以及实现期望结果的附加步骤。

石墨外延和化学外延都有其长处和短处。石墨沉淀利用成熟的工艺形成基底结构,通常需要较少的步骤才能获得最终的CD。然而,它要求沟槽的尺寸与键合对的BCP链长度完全匹配,任何线形图案的不规则性都可能出现在BCP结构中。

化学外延需要更少的空间来实现类似的CD,并且在设计上提供了更多的灵活性,因为它不需要与BCP链长度精确匹配。但它通常涉及更复杂和微妙的过程,包括使用特定的化学构图材料,这可能会使控制变得更具挑战性。化学外延也可能对表面能和聚合物-衬底相互作用的变化更敏感,如果不精确处理,可能会导致缺陷。

DSA的缺点是缺陷

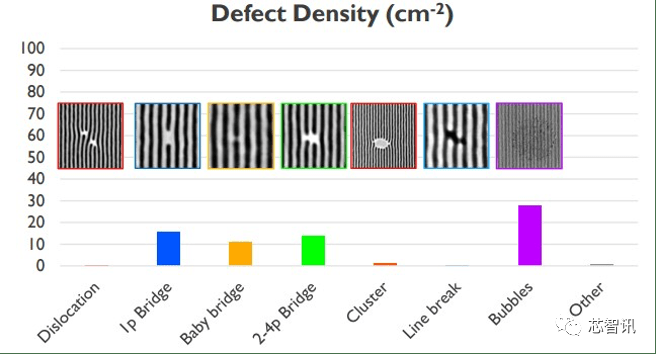

将DSA从实验室引入晶圆厂仍然主要受到缺陷控制的阻碍。尽管控制在过去三年中有了显著改善,但缺陷仍然太高,无法满足<1/cm2的行业标准。DSA中常见的缺陷包括线间桥接、线塌陷、气泡和线位错。位错是一个特别的挑战,因为它们在蚀刻或图案转移过程中无法去除(见图6)。

图6:使用 DSA 的 EUV 图案的 13nm/P28 不同缺陷的每平方厘米密度。来源:imec

DSA中的缺陷问题是复杂的,影响缺陷的因素很多。工艺相关的问题可能包括退火温度、蚀刻方法、剥离方法和所需的膜厚度,而BCP本身的纯度和成分等化学因素可能会引发问题。

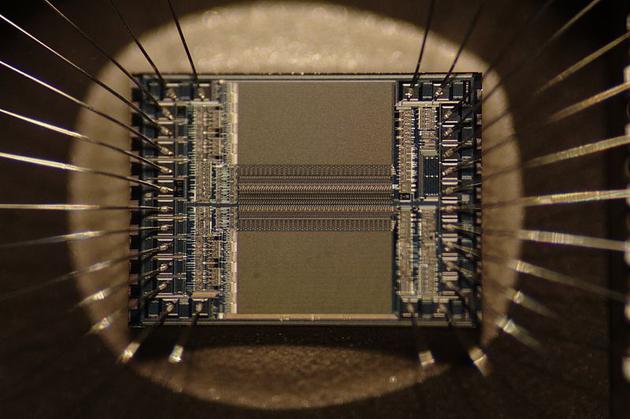

DSA过程的一个显著缺点是,它只能制作周期性的、简单的结构,例如空间中的线或孔,这使得它对常规存储器芯片更好,但对逻辑芯片来说更难。“如果一个器件有一个我们必须构建的结构,它必须是周期性的和简单的,”Hyo Seon Suh说。“这对DRAM来说很好,因为DRAM的结构是基本的,在高度重复的模式中是一致的。在逻辑器件的情况下,这是一个更随机的结构,所以结构的设计需要有DSA意识。”

其他人也表示同意。英特尔发言人表示:“DSA面临的最大挑战一直是缺陷以及如何使布局对DSA友好。”“几年来,英特尔一直与材料和工具供应商合作,将DSA缺陷降低到HVM级别,并与内部设计团队合作,使布局与DSA兼容。”

DSA检查和计量

DSA结构的尺寸计量也存在重大问题。DSA形成的图案缺乏化学对比度,这对测量的灵敏度提出了挑战。这些图案在转移到基板上(通过蚀刻)后可以更好地看到,但这严重限制了微调和校正的选择,导致成本高昂且耗时的返工,甚至报废整个批次。

CD-SEM图像主要用于识别DSA结构中的图案缺陷,但CD-SEM速度较慢,并且仅限于芯片上的几个样品位点,考虑到DSA的较高缺陷率,这是一个问题。此外,很少有数据集具有可供分析的比较监督模型。然而,imec的研究人员在6月发表了一篇论文,内容是使用SEM图像分析的机器学习(ML)模型,使用YOLOv8(一种最先进的神经网络)为六边形接触孔DSA图案的数据集获得完整的标签,该网络的精度超过0.9mAP(平均精度的90%)。[4]

根据多个来源,今天的DSA检查通常使用散射测量法进行。然而,imec的Dehaerne及其同事指出,DSA分析没有传统的自动缺陷检测软件。“基于机器学习的SEM图像分析已成为使用监督ML模型进行缺陷检测的一个越来越受欢迎的研究课题。”[4]

DSA的新兴用途

对计量学的研究只是DSA在半导体制造中突破性新应用的最新进展之一。韩国高级科学技术研究院的科学家们正在使用<10nm的BCP沿着石墨烯2D薄片的原子边缘进行自组装,以可靠地对线边缘和线宽粗糙度非常低的2D材料进行纳米图案化,形成具有开关特性的<10nm石墨烯纳米带阵列。

布鲁克海文国家实验室的科学家最近使用DSA在硅衬底上开发了一种超导薄膜量子材料(厚度<100nm)。他们的工艺可以在现有的半导体制造工艺中实现具有成本效益的大批量薄膜制造(HVM),这些工艺在几乎零能量损失的情况下表现出电转移。

结论

对于定向自组装技术热潮的重新出现来说,这是一个激动人心的时刻。DSA为193nm光刻和EUV光刻的较低节点的图案校正提供了一种可行的制造工艺,因为缺陷率正在降低,新的计量选项上线。最吸引人的是,它可以在不必购买EUV光刻机的情况下扩展193nm光刻。

在十年前有了一个充满希望的开端,随后在实验室里经历了多年的煎熬之后,DSA领域突然发展得更快。尽管DSA尚未用于生产,但对新工艺流程和更高质量聚合物的研究可以实现对重复结构中特征尺寸和图案的更精细控制。

编辑:芯智讯-浪客剑 来源:semiengineering.com

- M. Lapedus, “Directed Self Assembly Grows Up,” Semiconductor Engineering, March 21, 2013.

- G. Haley, “Challenges Grow for CD Sems and 5nm and Beyond,” Semiconductor Engineering, April 11, 2023.

- Douglas Guerrero, A Lithographer’s Guide to Patterning CMOS Devices with Directed Self-Assembly, SPIE Press (2020), http://dx.doi.org/10.1117/3.2567441

- E. Dehaerne, et al., “YOLOv8 for Defect Inspection of Hexagonal Directed Self-Assembly Patterns: A Data-Centric Approach,” 38th EMLC Conference (2023), arXiv:2307.15516

- 芯片制造行业的新方向:“自组装”技术解析,芯智讯