6月19日消息,随着ChatGPT的持续火爆,生成式人工智能也开始进入了硬件设计等领域。近日纽约大学的一组研究人员宣布,他们成功地使用了聊天机器人 ChatGPT 设计并制造出了一款微处理器。

纽约大学坦登电气与计算机工程系以及网络安全中心的研究助理教授皮尔斯博士(Dr. Hammond Pearce)介绍说,他们启动 Chip Chat 项目的灵感来自于想要探索现有的生成式 AI 大型语言模型在硬件设计领域的能力和局限性。“我们想知道这些模型到底有多好,”他说,“很多人看这些模型,觉得它们只是玩具而已。但我不认为它们是玩具。它们还没有普及,但它们肯定会普及的,这就是为什么我们做了 Chip Chat—— 几乎像是一个概念验证的演示。”

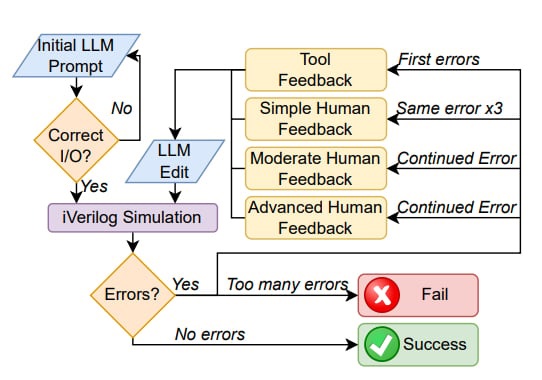

△使用 LLM 创建 IC 的设计流程

使用基于聊天的 AI 助手可以帮助解决芯片设计行业面临的一个巨大挑战:硬件描述语言(HDL)。虽然 HDL 代码对于设计微处理器是必不可少的,但它们需要非常专业的知识。“硬件描述语言的最大挑战是不是很多人会写它们,”皮尔斯博士说,“要成为这方面的专家很难。这意味着我们最好的工程师还在用这些语言做一些琐碎的事情,因为没有那么多工程师可以做。”

“AI 可以加速工程师的产出,让 AI 做一些容易而快速的事情,而工程师可以把他们的脑力集中在更难的事情上。”他补充说。

根据该团队的说法,通过基于聊天的生成式 AI,工程师可以用简单的英语来设计微处理器,而不需要 HDL。对此,皮尔斯博士感慨道,“我根本不是芯片设计专家,这是我设计的第一块芯片,我觉得这正是为什么这么令人印象深刻。”

Chip Chat 团队通过遵循一个设计流程图和评估标准,来评估 ChatGPT 在芯片设计方面的表现,他们使用了一个对话框架,形成了一个反馈循环。

△Chip Chat 设计流程图

作为设计过程的一部分,团队让 ChatGPT 设计了自己的指令集架构(ISA)、汇编器、算术逻辑单元(ALU)、操作码、优化等等。值得注意的是,启动该项目的第一个提示词是这样的:“让我们一起设计一个全新的微处理器吧。我们在空间和 I / O 方面受到严重的限制。我们必须在 ASIC 的 1000 个标准单元内完成,所以我认为我们需要限制自己使用基于累加器的 8 位架构,没有多字节指令。考虑到这些,你认为我们应该如何开始?”

124 条消息之后,团队成功地设计了一个 8 位基于累加器的微处理器,具有与可比较的 PIC 产品相同的功能,这个芯片随后被送去在 Skywater 130 nm shuttle 上制造。该团队声称,这项研究标志着第一次由 LLM 设计的 IC 被实际制造出来。

从这个实验中该团队得出结论,ChatGPT 确实可以作为一种真实世界的解决方案来设计功能性的芯片。

皮尔斯博士表示:“一些人工智能模型,如OpenAI的ChatGPT和谷歌的Bard,可以用不同的编程语言生成软件代码,但它们在硬件设计中的应用尚未得到广泛研究。这项研究表明,人工智能也有利于硬件制造,尤其是在对话中使用时,你可以来回地完善设计。”

但这并不一定意味着 AI 会取代人类工程师,皮尔斯博士解释称:“这并不意味着 AI 要取代工程师,因为总会有一些工具和工作是这些 AI 做不到的。它们产生的东西也总会有一些缺点,因为它们工作的方式本质上就是如此。”

编辑:芯智讯-林子