6月19日消息,据外媒Patently apple报道,全球晶圆代工龙头台积电最近已经开始准备为苹果公司及NVIDIA(英伟达)试产2nm的芯片。

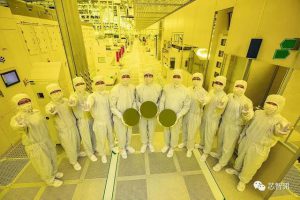

报道指出,三星电子于 2022 年 6 月率先宣布其基于GAA 技术3nm制程正式量产,成为全球首家量产3nm制程技术的企业。台积电虽然相比三星晚了6个月,在2022年底才正式量产3nm制程,但是台积电的3nm已经率先获得了大客户的采用,并且为了拉大与三星的差距,台积电近期已经启动了2nm试产的前置作业,开始准备为苹果和 NVIDIA 试产2nm产品。据悉,台积电将派遣约 1,000 名研发人员前往位于竹科正在建设中的 Fab 20 晶圆厂工作,目标是在2024年风险试产与2025年量产2nm。

值得注意的是,三星 DS 部门总裁 Kyung Kye-hyun 于 5 月初的一次演讲中表示,三星计划超越台积电,目标就是从比台积电更早的量产基于GAA 技术的2nm制程。

事实上,台积电除了先进制程之外,也通过先进封装技术来维持技术的领先。不久前,台积电就宣布先进封测六厂启用正式启用,成为台积电首家达成前后端制程 3DFabric 整合一体化自动化先进封测厂和测试服务工厂。同时,也为 TSMC-SoIC (系统整合芯片)制程技术的量产做准备。先进封测六厂的启用,将使台积电对 SoIC、InFO、CoWoS、先进测试等各项 TSMC 3DFabric 先进封装与硅堆叠技术,拥有更完整及灵活的产能规划之外,也带来更高的生产良率与效能协同效应。

台积电营运/先进封装技术暨服务、品质暨可靠性副总经理何军表示,微芯片堆叠是提升芯片性能与成本效益的关键技术,为应对强劲的三度积体电路 (3DIC) 市场需求,台积电已完成先进封装及硅堆叠技术产能的提前部署,通过 3DFabric 平台提供技术领先与满足客户需求产能,共同实现跨时代科技创新,成为客户长期信赖的重要伙伴。

除了台积电和三星之外,美国半导体大厂英特尔计划在2024年量产2nm,重新引领半导体制程技术。在在当地时间 6 月 1 日的线上活动中,英特尔还公布了其芯片背面电源解决方案 PowerVia 的技术发展、测试数据和路线图,开始扩大其在晶圆代工产业的影响力。相比之下,虽然目前台积电也在开发背面供电的技术,但要到 2026 年才会使用该技术。

此外,英特尔计划在2024 年下半年量产更为先进的1.8nm制程。今年3月,英特尔还制定了一项计划,就是借助与Arm 建立合作伙伴关系,加速1.8nm制程技术的量产。不过,市场人士也存在一些不确定看法,认为即使英特尔按照路线图取得成功,但最终要达到收支平衡,对公司来说仍是一个很大的挑战。

编辑:芯智讯-浪客剑