10月28日消息,晶圆代工龙头大厂台积电27日宣布,成立开放创新平台 3D Fabric 联盟,推动 3D 半导体发展,目前已有 19 个合作伙伴同意加入,包括美光、三星记忆体及 SK 海力士。

这一联盟是台积电第六个开放创新平台(OIP)联盟。台积电表示,3D Fabric 联盟将协助客户达成芯片及系统级创新的快速实作,并且采用台积电由完整的 3D 硅堆迭与先进封装技术系列构成的 3D Fabric 技术来实现次世代的高效能运算及行动应用。

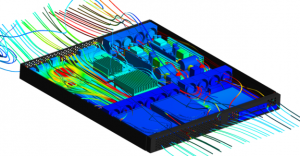

目前,大多数高端处理器是单片式的,但随着前沿制造技术的使用成本越来越高,设计方法正在转向多芯片模块。在未来的几年里,多芯片系统封装(SiPs)预计将变得更加广泛,先进的 2.5D 和 3D 芯片封装技术将变得更加重要。

虽然多芯片 SiP 有望简化高度复杂设计的开发和验证,但它们需要全新的开发方法,因为 3D 封装带来了许多新的挑战。这包括 3D 集成所需的新的设计流程、新的电力输送方法、新的封装技术和新的测试技术。为了充分利用台积电 2.5D 和 3D 封装技术(InFO、CoWoS 和 SoIC)的优势,芯片开发行业需要整个生态系统在芯片封装方面协同工作,而这正是 3DFabric 联盟的目的所在。

台积电研究员、设计与技术平台副总裁卢立中博士说:“三维硅堆叠和先进的封装技术为芯片级和系统级创新的新时代打开了大门,同时也需要广泛的生态系统合作,以帮助设计者在无数的选择和方法中找到最佳路径。”

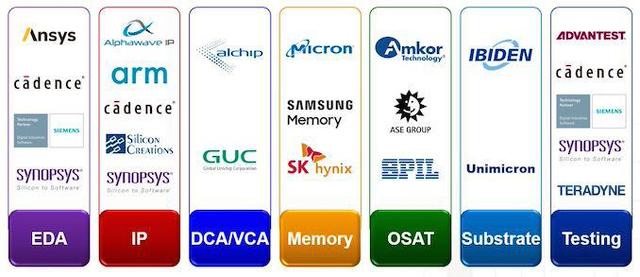

台积电的 3DFabric 联盟汇集了电子设计自动化(EDA)工具的开发者、知识产权供应商、合同芯片设计者、存储器制造商、先进的基材生产商、半导体装配和测试公司以及用于测试和验证的设备制造集团。该联盟目前有 19 个成员,但随着时间的推移,预计会有更多新成员加入。

作为联盟的领导者,台积电将制定某些基本规则和标准。同时,3DFabric 联盟的成员将共同定义和共同开发台积电 3D Fabric 技术的一些规范,将率先获得台积电的 3D Fabric 路线图和规范,以使他们的计划与晶圆厂的计划以及联盟其他成员的计划保持一致,并能够设计和优化与新封装方法兼容的解决方案。

最终,台积电希望确保 3D Fabric 联盟的成员将为其客户提供兼容和可互操作的解决方案,以便快速开发和验证使用 2.5D 和 3D 封装的多芯片 SiP。

例如,为了用合格的 EDA 工具和流程统一设计生态系统,台积电开发了其 3Dblox 标准。3Dblox 涵盖了构建采用 2.5D 和 3D 封装方法的多芯片器件的各个方面(如芯片和接口定义),包括物理实现、功耗、散热、电迁移 IR 降(EMIR)和定时 / 物理验证。

最终,台积电设想,该联盟将大大简化和精简开发更先进芯片的过程,特别是对那些更依赖外部 IP / 设计的中小型公司。例如,

虽然像 AMD 和 Nvidia 这样的大公司倾向于开发自己的 IP、互连和封装技术,但多芯片 SiP 有望使小公司也能开发复杂的芯片式处理器。对他们来说,标准的第三方 IP、快速上市和适当的集成是成功的关键,所以 3D Fabric 联盟对他们来说至关重要。