4月17日消息,据外媒naver报道,苹果公司正在台积电小量试产最新3D小芯片堆叠技术SoIC(系统整合芯片),最快有望2025~2026年有机会看到终端产品问世。

11月28日-29日,由合肥市人民政府指导,合肥市投促局、庐江县政府主办,高工移动机器人、高工机器人产业研究所(GGII)承办的2023(第四届)高工移动机器人年会暨高工金球奖颁奖典礼在合肥隆重举行。本次大会以“智造物流大升级 群雄逐鹿新时代”为主题,超200家移动机器人产业链上下游企业出席,共同探讨制造物流革新的机遇与挑战。

7月14日消息,根据外媒报导,IBM与日本半导体设备大厂东京电子于近日宣布,在3D芯片堆叠方面获得了新得技术突破,成功运用了一种新技术将3D芯片堆叠技术用于的12 吋晶圆上。由于芯片堆叠目前仅用于高阶半导体产品,例如高带宽内存(HBM) 的生产。不过,在IBM 与东京电子提出新的技术之后,有机会扩大3D芯片堆叠技术的应用。

4 月 1 日消息,据日经中文网报道,佳能正在开发用于半导体 3D 技术的光刻机。佳能光刻机新品最早有望于 2023 年上半年上市。曝光面积扩大至现有产品的约 4 倍,可支持 AI 使用的大型半导体的生产。

当地时间3月21日,加利福尼亚州圣克拉拉讯 – AMD(超威)宣布推出世界首款采用3D芯片堆叠的数据中心CPU,即采用AMD 3D V-Cache技术的第三代AMD EPYC(霄龙)处理器,代号“Milan-X(米兰-X)”。这些处理器基于“Zen 3”核心架构,进一步扩大了第三代EPYC处理器系列产品,相比非堆叠的第三代AMD EPYC处理器,可为各种目标技术计算工作负载提供高达66%的性能提升。

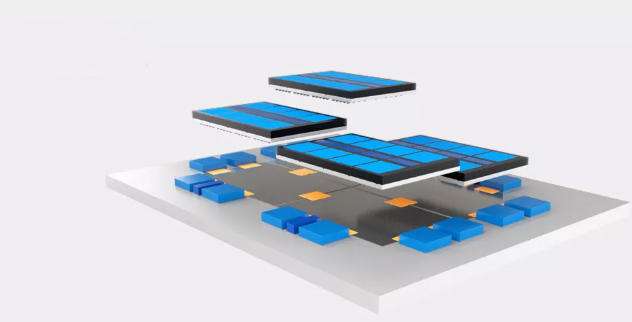

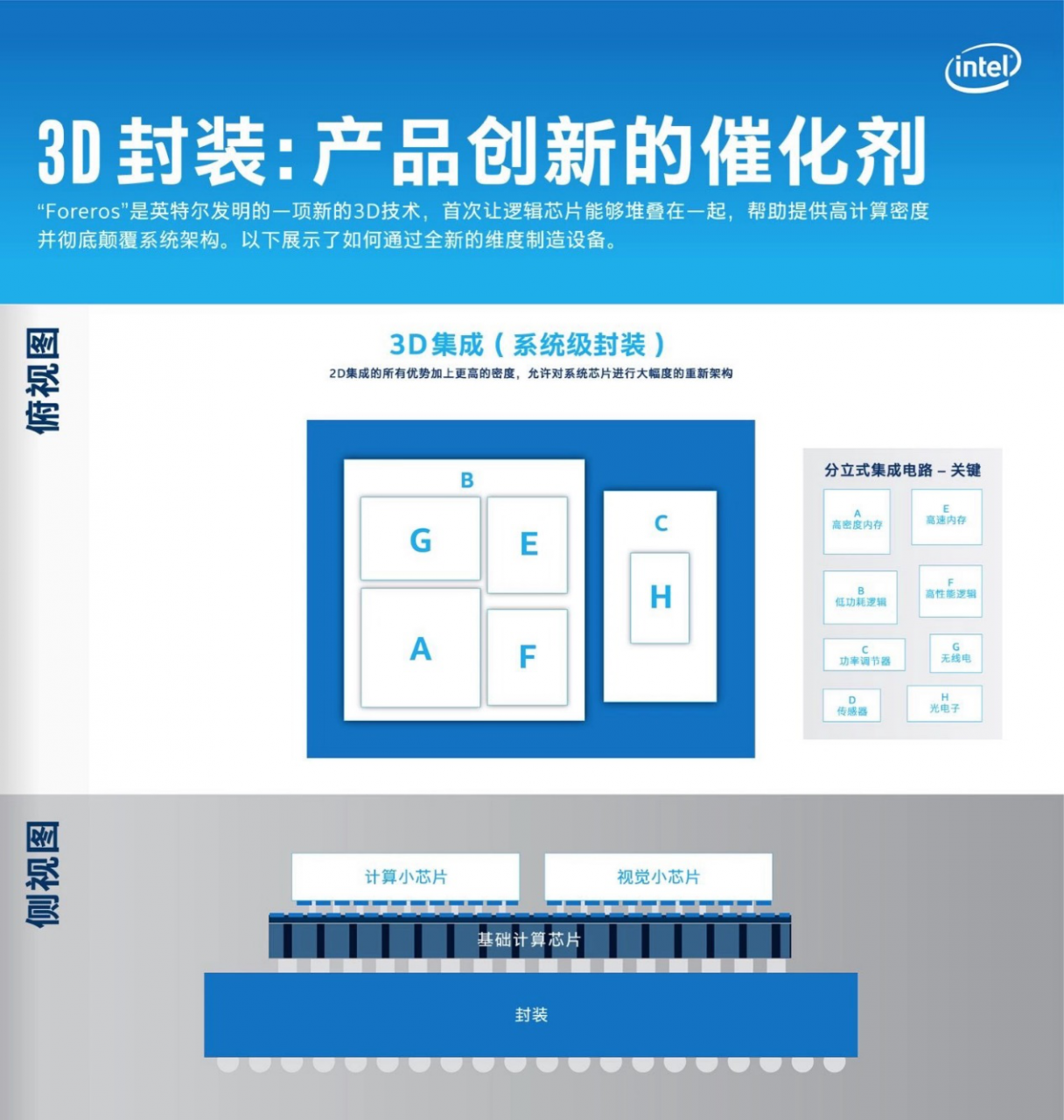

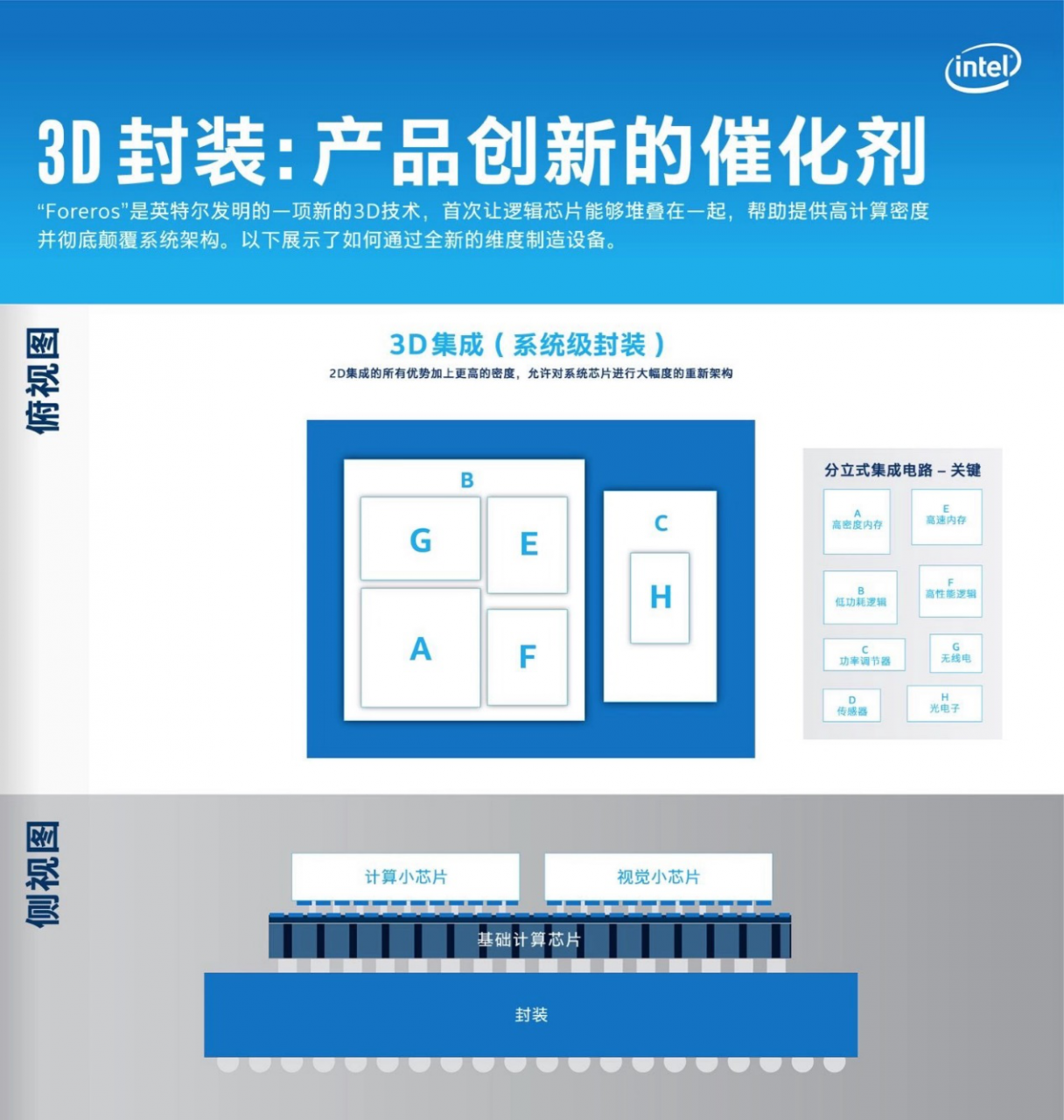

英特尔是全球半导体行业的引领者,以计算和通信技术奠定全球创新基石,塑造以数据为中心的未来,英特尔一直在不断追求创新发展。在近日举行的英特尔“架构日”活动中,英特尔不仅展示了基于10纳米的PC、数据中心和网络系统,支持人工智能和加密加速功能的下一代“Sunny Cove”架构,还推出了业界首创的3D逻辑芯片封装技术——Foveros。这一全新的3D封装技术首次引入了3D堆叠的优势,可实现在逻辑芯片上堆叠逻辑芯片。

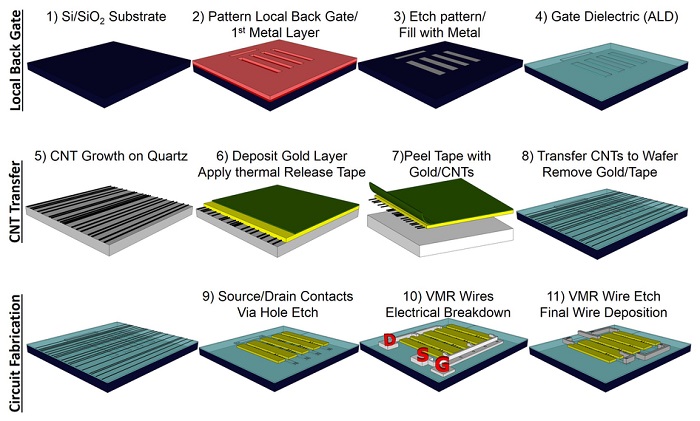

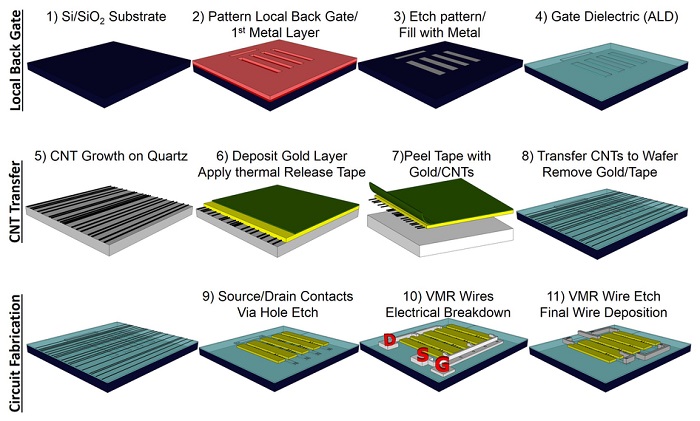

为了追赶摩尔定律,麻省理工与斯坦福两所大学的计算机科学家和电气工程师们,携手开发出了一种集成了内存和处理器、并采用碳纳米管线来连接的 3D 计算芯片。该团队制造了一台小规模的碳纳米管(CNT)计算机,它能够运行程序、简单的多任务操作系统、以及执行 MIPS 指令。项目领导人 Max Shulaker 相信,该技术能够克服逻辑电路和内存之间的通讯瓶颈。