虽然在半导体先进制程工艺方面,近日三星成功抢先台积电量产了3nm GAA制程工艺,但是在2.5/3D先进封装技术方面,三星仍落后于英特尔和台积电。而为了缩短这方面的差距,三星也已经组建了新的半导体封装工作组发力先进封装技术。

据韩国媒体BusinessKorea报导,三星DS 部门已于6月中旬组建了半导体封装工作组,由直属DS 部门CEO Kyung Kye-hyun直接管辖。该半导体封装工作组由DS 部门测试与系统封装(TSP) 工程师、半导体研发中心研究人员及存储和代工部门相关人员组成,预计将推出先进封装解决方案,加强与有着封装业务需求的大型代工客户合作。

报道称,三星此举代表其对于先进封装技术的重视程度。特别是在目前先进制程工艺微缩越来越困难,成本也越来越高的背景之下,通过先进封装技术将多个芯片进行异质整合,或将传统大芯片拆分成多个小芯片通过先进封装技术进行整合的Chiplet方案,成为了新的方向。而这其中,先进封装技术则是关键。

根据市场研究公司Yole Development的报告显示,英特尔和台积电分占2022 年全球先进封装投资32% 和27%,三星仅排名第四,甚至落后台湾封装测试大厂日月光投控。

早在2017年英特尔就推出了EMIB(Embedded Multi-Die Interconnect Bridge,嵌入式多核心互联桥接)封装技术相结合,可以将不同类型、不同制程的小芯片IP以2.5D的形式灵活组合在一起,形成一个类似SoC的结构。

2018年底,英特尔又推出了业界首创的3D逻辑芯片封装技术——Foveros 3D,它可实现在逻辑芯片上堆叠不同制程的逻辑芯片。以前只能把逻辑芯片和存储芯片连在一起,因为中间的带宽和数据要求要低一些。而Foveros 3D则可以把不同制程的逻辑芯片堆叠在一起,裸片间的互联间隙只有50μm,同时可保证连接的带宽足够大、速度够快、功耗够低,而且3D的堆叠封装形式,还可以保持较小的面积。2020年,英特尔推出了基于Foveros 技术生产的代号为“Lakefield”的处理器。2021年7月,英特尔还宣布计划推出Foveros Direct技术,可以实现10微米以下的凸点间距,使3D堆叠的互连密度提高一个数量级。

除了英特尔之外,台积电在先进封装领域也布局多年。目前,台积电已将2.5D和3D先进封装相关技术整合为“3DFabric”平台,可让客户们自由选配,前段技术包含3D的整合芯片系统(SoIC InFO-3D),后段组装测试相关技术包含2D/2.5D的整合型扇出(InFO)以及2.5D的CoWoS系列家族。值得一提的是,台积电还在日本筑波建了3D IC研发中心,该研发中心已于今年6月24日开始启用。

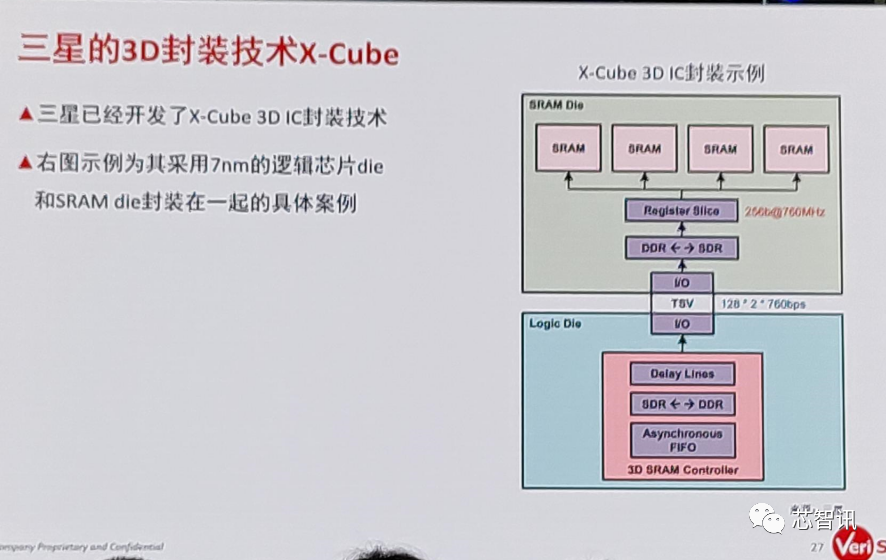

虽然三星较早也推出了2.5D封装技术I-Cube,可将一个或多个逻辑晶片(如CPU、GPU 等) 和多个存储芯片(如高频宽存储器、HBM) 整合连结放置在硅中介层( Interposer) 的顶部,进一步使多个芯片为整合为单个元件工作。2020年8月,三星又宣布推出了新一代3D封装技术——X-Cube,基于TSV硅穿孔技术将不同芯片堆叠,比如可以将SRAM堆叠到芯片上方,释放了占用空间,可以堆叠更多内存芯片,目前已经可以用于7nm及5nm工艺。但是,不论是从技术领先性和商用情况来看,三星在先进封装技术方式仍落后于英特尔和台积电。

值得注意的是,三星除了2020 年推出3D封装技术“X-Cube”之外,三星DS 部门还曾在2021 年6 月的Hot Chips大会上表示,正在开发3.5D 先进封装技术,但是三星并未透露具体的细节。

此次三星先进封装工作组的成立,显然意味着三星将进一步加大对于先进封装技术的投入,但是能否成功找到方法,缩小与英特尔、台积电在先进封装领域的差距,将是市场关注的重点。

相关文章:《台积电2.5/3D先进封装布局详解》

编辑:芯智讯-浪客剑