近日,业内盛传英伟达(NVIDIA)正在考虑将全新的拥有诸多优势的 CoWoP(Chip-on-Wafer-on-Platform PCB)作为其下一个封装解决方案,可能将会率先导入其下一代 Rubin GPU 使用。不过,摩根士丹利的一份报告称, 虽然英伟达可能正在开发CoWoP技术,但短期内不太可能大规模应用。

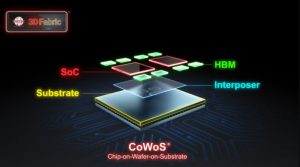

目前众多的HPC芯片和AI芯片的首选先进封装解决方案是台积电的CoWoS(Chip‑on‑Wafer‑on‑Substrate),这是一种比较成熟的 2.5D 封装技术,是通过将硅片(例如Logic + HBM)并排贴在一个硅中介层(Si Interposer)上,再焊接到封装基板(Package Substrate),然后用 BGA 焊球连接到主板。所有 CoWoS 解决方案的中介层面积均在增加,以便整合更多先进芯片和高带宽存储器的堆叠,以满足更高的性能需求。英伟达和AMD等人工智能大厂的AI芯片都有广泛采用CoWoS先进封装技术。

根据曝光的一份蓝图显示,英伟达计划与供应链厂商合作研发导入全新的CoWoP封装技术,以期替代当前的CoWoS的技术,预计2026年10月将率先在英伟达 GR150(Rubin)GPU平台上实现。

那么,相比传统的CoWoS技术来说,CoWoP技术有何不同呢?

简单来说,CoWoP技术就是“CoWoS减去封装基板”,即将硅片与硅中介层组合后,直接键合在强化设计的主板(Platform PCB)上,省去传统的封装基板与BGA步骤,形成“芯片-硅中介层-PCB”的一体化结构,实现了更薄、更轻、更高带宽的模块设计,同时充分利用大尺寸PCB产线的高产能与成熟工艺。但是需要指出的是,强化设计的主板需直接承担高精度信号与电源布线的功能。虽然,“删减封装基板”看似容易,但在技术层面上实现则难度相当高。

英伟达企图再建构护城河,CoWoP带来七大优势

供应链业者表示,英伟达正计划通过CoWoP将原本集中于芯片制程的性能瓶颈,转移至封装与系统级互连,以此建立新的技术护城河。整体而言,目标就是通过高度系统整合与平台定义权,主导未来AI芯片的标准。

根据曝光的CoWoP蓝图显示,CoWoP未来可带来“七大优势”,包括:

1、信号完整性(SI)提升:省去一层封装基板,通过硅中介层实现芯片与PCB的微凸点倒装互连,信号传输路径更短、更直接,NVLink和HBM通信损耗显著降低,传输距离可延长。

2、电源完整性(PI)强化:在CoWoS等传统封装中,电压调节器(Voltage Regulator,例如为GPU芯片提供稳定供电的电源管理模块)通常位于PCB主板或封装基板(Substrate)上,与GPU裸片之间存在较长的供电路径,这会引入寄生电阻、电容和电感(统称“寄生参数”),导致供电损耗、电压波动及响应延迟。而CoWoP架构则可以使得电压调节器可集成到更靠近GPU裸片的位置,大幅缩短供电路径,以减少寄生参数,使电压更稳定,降低噪声干扰,显著改善GPU在高负载下的供电效率。

3、散热性能提升:减少供电损耗意味着更少的热量产生,结合CoWoP的“无盖设计”(Lidless),使散热器可直接接触GPU裸片,进一步提升散热效率。

4、降低PCB热膨胀系数,解决翘曲问题。

5、改善电迁移(Electromigration)。

6、降低ASIC成本与设计复杂度。省去了传统封装中昂贵的ABF/BT有机基板和BGA焊球环节,既降低材料成本(无封装、无盖子),也简化了制造流程。

7、支持更弹性的芯片模块整合方式,迈向无封装构架长期愿景。

根据业界预计,CoWoP用大尺寸PCB面板替代了单价高昂的ABF基板(传统基板占封装成本40%以上),再加上无需BGA焊球、无盖子,整体可以使得成本降低30%-50%,并且利用成熟的PCB产线可以缩短交付周期。而且,PCB扩产周期仅需6-12个月,远低于传统基板的2年,可快速响应AI算力设备爆发需求。

CoWoP带来的四大挑战

虽然CoWoP相比CoWoS拥有诸多优势,但是也带来了四大挑战:

1、主板技术门坎大幅提高:Platform PCB必须具备封装等级的布线密度、平整度与材料控制。PCB在此不仅承担电连接,还需要通过HDI或MSAP/SAP等工艺在板上形成精细的重分布层(RDL),来保证信号完整性与功率分配。比如,需要再同一板上完成多至12层、30μm级线宽/线距的高速互连,兼具高带宽、低延迟与设计灵活性。

2、返修与良率压力剧增,GPU裸晶直接焊接主板,失败即报废,制程容错空间低。

3、系统协同设计更复杂,增加开发成本。

4、技术转移成本高。

供应链认为,CoWoP技术若顺利推进,主板转变为芯片的“最后一层封装”,不仅能降低整体成本,更将主导AI硬件平台的定义权。不过也仍有PCB业者认为,目前载板技术相对成熟,价格合理,CoWoP欲取代传统封装,仍需时间。

尽管如此,目前曝光的CoWoP技术蓝图数据仍显示,CoWoP技术已在2025年7月,被列入称为GB100的内部测试平台中,预计2026年10月在GR150平台上,实现CoWoS与CoWoP并行封装策略。

显然,这里的GB100、GR150都是英伟达内部工程测试样品,例如用上一代Grace CPU,搭配Blackwell GPU平台或新一代的Rubin GPU平台,进行先进封装技术的各种研发,并不一定会商品化对外销售。

业界预计,英伟达将与台积电、日月光集团旗下的矽品,以及PCB、设备等供应链厂商在2025年9月的供应链论坛后,将共同研究讨论基于CoWoP的450mm×450mm封装的可行性设计。

大摩“泼冷水”

摩根士丹利最新的研报称,英伟达的Rubin和Rubin Ultra仍将沿用现有的ABF基板技术,而非转向CoWoP方案。而且Rubin Ultra的ABF基板相比Rubin规格更大且层数更多,这与CoWoP的技术路径背道而驰。

摩根士丹利分析师认为,从CoWoS转向CoWoP在技术上仍面临重大挑战,对ABF基板的依赖短期内难以改变。因为,技术转换的复杂性和供应链重组风险使得短期内大规模采用CoWoP并不现实。

比如,CoWoP技术要求PCB(印刷电路板)的线/间距(L/S)缩小至10/10微米以下,这与目前ABF基板的标准相当。当前高密度互连(HDI) PCB的L/S为40/50微米,即使是用于iPhone主板的类基板PCB(SLP)也仅达到20/35微米,要将PCB的L/S从20/35微米缩小到10/10微米以下存在显著技术难度。

大摩分析师Howard Kao指出,这一技术壁垒是英伟达Rubin Ultra不太可能采用CoWoP的主要原因之一。除了技术的复杂性之外,从CoWoS转向CoWoP将带来显著的良品率风险和相关供应链的重组。目前台积电的CoWoS良品率已接近100%,在如此高的良品率基础上进行技术切换存在不必要的风险。而且,考虑到目标产品将在一年内进入量产,这种技术转换在商业逻辑上并不合理。

不过,摩根士丹利表示,尽管短期内不太可能大规模应用,但鉴于CoWoP的技术优势,不排除英伟达正在并行开发CoWoP技术的可能性,作为当前量产技术的补充,以应对基板翘曲问题、解决特定封装材料供应紧张或简化GPU板制造工艺。

编辑:芯智讯-浪客剑