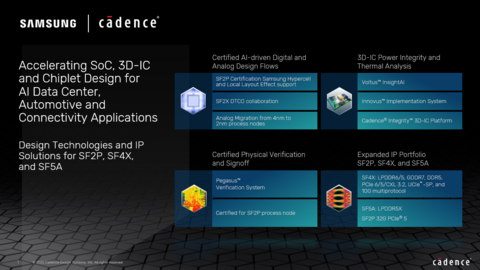

当地时间6月16日,EDA大厂Cadence在美国加州圣何塞宣布与 Samsung Foundry 达成合作,包括一项新的多年 IP 协议,以扩展 Samsung Foundry 的 SF4X、SF5A 和 SF2P 先进工艺节点中的 Cadence 存储器和接口 IP 解决方案。为了进一步加强持续的技术合作,两家公司正在利用 Cadence 的 AI 驱动设计解决方案和三星先进的 SF4X、SF4U 和 SF2P 工艺节点,为 AI 数据中心、汽车(包括高级驾驶辅助系统 (ADAS))和下一代 RF 连接应用提供高性能、低功耗的解决方案。

Cadence 的 AI 驱动型设计解决方案以及全面的 IP 和芯片解决方案组合可提高设计人员的工作效率,并加快采用先进 Samsung Foundry 工艺的尖端 SoC、小芯片和 3D-IC 的上市时间 (TTM)。

“我们支持 Samsung Foundry 工艺节点上的完整 IP、子系统和小芯片组合,我们最新的多年 IP 协议加强了我们持续的合作,”Cadence 高级副总裁兼芯片解决方案事业部总经理 Boyd Phelps 表示。通过将 Cadence 的 AI 驱动设计和芯片解决方案与 Samsung 的先进工艺相结合,我们正在提供共同客户创新所需的领先技术,并更快地将他们的产品推向市场。

三星电子副总裁兼代工设计技术团队负责人 Hyung-Ock Kim 补充道:“Cadence 从 RTL 到 GDS 的数字工具套件现已获得三星最新 SF2P 工艺节点的认证,支持 Hyper Cell 和 LLE 2.0 技术等进步。Cadence 和 Samsung 还密切合作,使用 GPU 加速实现模拟迁移,增强电源完整性,并改进 3D-IC 的热和翘曲分析。此外,Cadence 和 Samsung Foundry 之间达成了一项多年协议,旨在扩展内存和接口 IP 解决方案,进一步加强了我们的合作伙伴关系。

扩展的 IP 协议

Cadence 和 Samsung Foundry 签署了一项新的多年期协议,为人工智能、高性能计算 (HPC) 和汽车应用提供先进的存储器和接口 IP 解决方案。扩展的 SF4X IP 产品组合包括 LPDDR6/5x-14.4G、GDDR7-36G、DDR5-9600、PCI Express (PCIe) 6.0/5.0/CXL 3.2®®,通用小芯片互连 Express™(UCIe™)-SP 32G以及 10G 多协议 PHY(USB3.x、DP-TX、PCIe 3.0 和 SGMII)以及配套控制器 IP,可实现完整的子系统硅解决方案。为汽车应用量身定制的 LPDDR5X-8533 PHY IP 完善了 SF5A IP 平台解决方案,在现有 SF2P 产品中增加新的 32G PCIe 5.0 PHY 可满足领先的 AI/HPC 客户的需求。

数字化全流程认证和先进数字化技术发展

基于广泛的设计和技术协同优化 (DTCO) 项目,Cadence 数字全流程已通过最新的 Samsung SF2P 工艺节点认证,包括 Samsung Hyper Cell 方法。此外,Cadence 还实现了对 Samsung Local Layout Effect (LLE) 时序精度的支持。Cadence 和 Samsung 还在 DTCO 上合作开发下一代工艺节点。

这Cadence 飞马™验证系统已通过 Samsung SF2P 和其他 Samsung 节点的认证。Cadence 物理验证流程经过优化,允许共同客户使用大规模可扩展性实现签核准确性和运行时目标,从而实现更快的 TTM。

模拟设计迁移

Cadence 和 Samsung Foundry 已成功将基于模拟单元的 4nm IP 自动迁移到先进的 2nm 工艺节点,在保持功能和设计意图的同时实现更快的周转时间。这种迁移凸显了技术扩展和 IP 重用对于节省时间和开发成本的重要性,并为模拟单元和其他 IP 在未来跨各种工艺节点的迁移奠定了基础。

射频芯片/封装协同设计参考流程协同

Cadence 和 Samsung Foundry 还成功展示了基于三星 14nm FinFET 工艺的下一代毫米波应用的全面前端模块 (FEM)/天线级封装 (AiP) 协同设计流程。通过简化 IC/模块开发每个阶段之间的设计数据管理,从初始系统级预算到 RFIC/封装协同设计、分析和版图后验证,加快了设计周转时间。

3D-IC 的电源完整性

Cadence 和 Samsung 合作对 3D-IC 进行了全面的全流程电源完整性分析,涵盖从早期探索到最终签核的整个过程,并采用了先进的 Cadence EDA 工具,包括伏特斯™洞察人工智能这创新™实施系统和正直™3D-IC 平台.Voltus InsightAI 应用于使用三星 SF2 节点的高速 CPU 芯片,实现了令人印象深刻的 80-90% 的 IR 压降违规分辨率,同时对时序和功耗的影响最小,展示了其平衡电源完整性与性能需求的能力。