5月19日消息,据路透社报道,比利时微电子研究中心(imec)将于当地时间20日在比利时安特卫普召开年度季度论坛,在此之前,imec首席执行官 Luc Van den Hove 近日通过一份声明呼吁半导体行业采用三维可重构 AI 芯片,以应对快速变化的 AI 软件。

Van den Hove 在声明中表示,AI 算法开发的速度比当前开发专用 ASIC 以解决 AI 数据流和计算中的特定瓶颈的策略要快。比如,专用集成电路可能需要一两年的时间来开发,并需要六个月的时间在晶圆厂进行制造。

“资产搁浅存在巨大的固有风险,因为当 AI 硬件最终准备就绪时,快速发展的 AI 软件社区可能已经发生了不同的转变,” Van den Hove 说到。

因此,Van den Hove 提议业界转向三维、可编程的 AI 计算处理单元阵列。

目前英伟达是全球最大 AI 芯片供应商,其提供的面向AI的GPU,具有足够的通用性,可以解决已开发的多种类型的 AI 算法。它还通过其强大的CUDA 并行计算平台和编程模型建立起了牢固的护城河。但是,英伟达的 GPU 也不是特定算法最节能的解决方案。因此,超大规模企业和其他人一直在寻求开发 ASIC 加速器,以解决数据中心中的特定工作负载集。

Van den Hove 说,虽然大公司可能能够负担得起,但对大多数公司来说,并不经济,且具有风险。

随着 AI 的前线从 LLM 转向多模式代理 AI,算法变革的步伐甚至可能正在加快。Van den Hove 提议,未来的 AI 芯片将多种 AI 计算样式构建块处理元件分组,即所谓的超级单元。然后,可编程的片上网络将能够链接和编程资源,以动态地满足算法要求。该方法将利用 3D 堆叠和其他先进的封装方法。

路透社所描述的内容听起来让人想起现场可编程门阵列(FPGA),但在更高的抽象级别上,可能以丰富多样的内存计算处理元素作为阵列中的构建块。

虽然这种方法似乎有道理,但应该注意的是,如果 AI 算法需求始终偏离组件超级单元中支持的某些计算样式,那么“AI 的 FPGA”将包含冗余芯片,并成为一种昂贵但节能且高性能的解决方案。平衡性能、功耗和面积 (PPA) 是芯片设计人员面临的持续挑战。传统上,选择 FPGA 是为了缩短上市时间,但体积更大,成本更高。

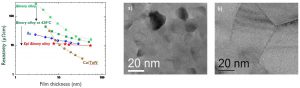

近几十年来,imec 一直是世界领先的半导体研究中心,并与领先公司合作开展竞争前项目。这使得imec能够提出和评估现在在前沿采用的许多技术。这些包括 FinFET、全能栅极晶体管、背面配电、小芯片。

编辑:芯智讯-浪客剑