12月3日消息,据芯智讯获悉,阿里巴巴旗下达摩院计算技术实验室成功研发全球首款基于DRAM的3D键合堆叠存算一体AI芯片。该芯片可突破冯·诺依曼架构的性能瓶颈,满足人工智能等场景对高带宽、高容量内存和极致算力的需求。在特定AI场景中,该芯片性能提升10倍以上,能效比提升高达300倍。

达摩院存算一体芯片(芯智讯拍摄)

为何研发存算一体芯片?

从计算机诞生起,计算机系统就是在冯·诺依曼架构下运行。在冯·诺伊曼架构中,计算与内存是分离的,计算单元从内存中读取数据,计算完成后再存回内存。特别是随着人工智能等对性能要求极高的场景爆发,传统的冯·诺依曼架构的短板开始凸显,例如功耗墙、性能墙、内存墙的问题。

造成这一问题的原因主要有两点:

一是数据搬运带来了巨大的能量消耗。数据显示,在传统架构下,数据从内存单元传输到计算单元需要的功耗是计算本身的约200倍,因此真正用于计算的能耗和时间其实占比很低。

二是内存性能的发展远远滞后于处理器的发展。目前,处理器的算力以每两年3.1倍的速度增长(AI对于算力的需求每两年提升750倍),能够处理器的数据量也快速增长,但是内存的性能每两年只有1.4倍的提升。

也就是说,即使处理器每秒能够处理3.1倍的数据量,但是由于处理器从内存中存取数据都是经过同一条内存总线访问,而这个内存总线如果最多只能通过1.4倍的数据量,这也意味着处理器也只能处理1.4倍的数据量。内存性能限制了处理器性能的提升。

目前内存性能的提升速度严重滞后于处理器性能提升的速度,这就好比一个漏斗,宽的一端是处理器,而狭窄的一端则是存储器,后者的性能极大地影响了数据传输的速度,这也被认为是传统计算机的阿克琉斯之踵。这一点在AI/HPC计算领域尤为明显。

如果要突破内存墙的瓶颈,就需要一个很好的从系统到芯片的硬件解决方案。而存算一体芯片则是目前解决该问题的最佳途径。

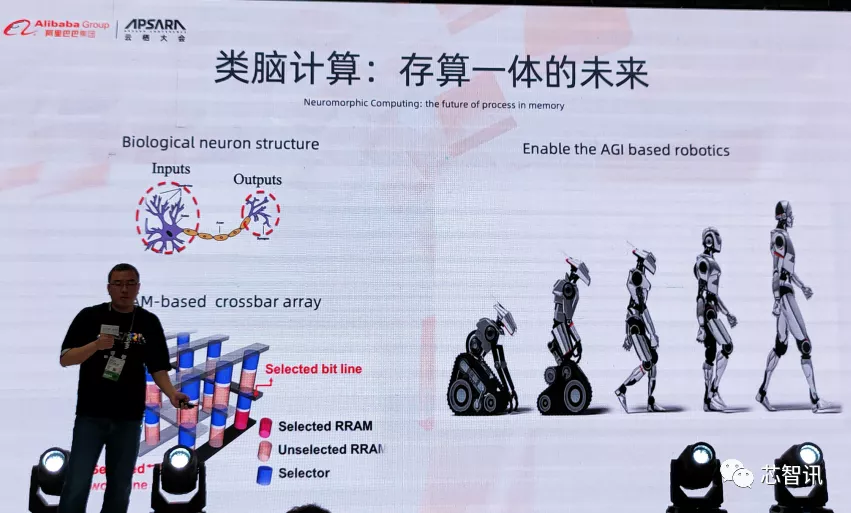

存算一体芯片的架构类似于人脑,将数据存储单元和计算单元融合为一体,大幅减少数据搬运,从而极大提高计算并行度和能效。这一技术早在90年代就被提出,但受限于技术的复杂度、高昂的设计成本,以及缺少应用场景,过去几十年业界对存算一体芯片的研究进展缓慢。随着AI场景的爆发,业界迫切需要该技术来解决算力瓶颈,达摩院希望通过自研创新技术解决业界难题。

如何实现“存算一体”?

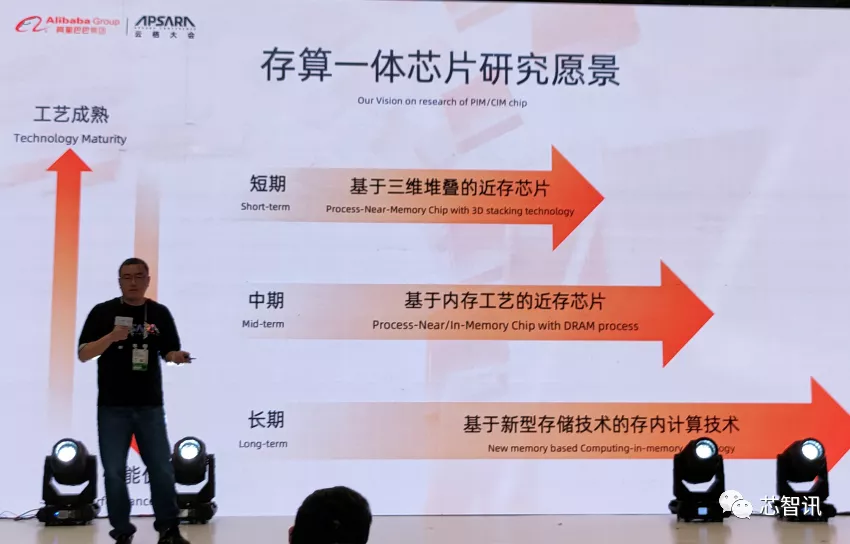

目前实现“存算一体”主要有三种技术路线:

1. 近存储计算(Processing Near Memory):计算操作由位于存储芯片外部的独立计算芯片完成。

2. 内存储计算(Processing In Memory):计算操作由位于存储芯片内部的独立计算单元完成,存储单元和计算单元相互独立存在。

3. 内存执行计算(Processing With Memory):存储芯片内部的存储单元完成计算操作,存储单元和计算单元完全融合,没有一个独立的计算单元。

其中,近存计算通过将计算资源和存储资源距离拉近,实现对能效和性能的大幅度提升,被认为是现阶段能解决内存墙问题的最佳途径。达摩院本次也是沿着这一方向进行突破。

达摩院有哪些技术创新?

目前HBM是将内存和计算结合在一起的主要方案之一,但该技术受限于单位容量带宽不足和功耗高的缺点,无法有效解决内存墙问题。

而混合键合(Hybrid Bonding)的3D堆叠技术拥有高带宽、低成本的特点,被认为是低功耗、近存计算的完美载体之一。

此次,达摩院研发的芯片首次采用混合键合(Hybrid Bonding)的3D堆叠技术——将逻辑计算芯片和DRAM存储芯片face-to-face地用特定金属材质和工艺进行互联,实现了炒高片上内存带宽,炒高密度片间互联。

最终的测试芯片显示,这种存算技术和架构的优势明显,能通过拉近存储单元与计算单元的距离增加带宽,降低数据搬运的代价,缓解由于数据搬运产生的瓶颈,而且与数据中心的推荐系统、图神经网络、大规模NN训练,对于带宽/内存的需求完美匹配。

据芯智讯此前在云栖大会“前沿计算技术突破论坛”上的了解的信息显示,该存算一体芯片的片上内存带宽可高达37.5GB/s/mm²,相比传统芯片,可提供

20倍以上片上内存容量和100倍以上内存能效比提升。在典型的实际应用中,可实现10倍以上的性能提升和300倍的能效提升。

在设计方面,该芯片内存单元采用异质集成嵌入式DRAM,拥有超大内存容量和超大带宽优势;计算芯片方面,达摩院研发设计了流式的定制化加速器架构,对推荐系统进行“端到端”加速,包括匹配、粗排序、神经网络计算、细排序等任务。这种近存架构也有效解决了带宽受限的问题,最终内存、算法以及计算模块完美融合,大幅提升带宽的同时还实现了超低功耗,展示了近存计算在数据中心场景的潜力。

得益于技术的创新性,该芯片的研究成果已被ISSCC 2022收录。目前,达摩院在存算一体架构方向上拥有大量领先成果,在ISCA、MICRO、HPCA等顶级计算机体系结构会议上发表多篇论文。

存算一体芯片在海量数据计算场景中拥有天然的优势,在终端、边缘端以及云端都有广阔的应用前景。例如VR/AR、无人驾驶、天文数据计算、遥感影像数据分析等场景中,存算一体芯片都可以发挥高带宽、低功耗的优势。从长远来看,存算一体技术还将成为类脑计算的关键技术。

针对这一技术未来有何研发和应用规划?

目前,整个行业对存算一体芯片技术的研究依旧处于探索阶段,在工艺成熟度、典型应用、生态系统等方面仍不成熟,达摩院希望逐步攻克技术难题,我们先研究基于三维堆叠的近存芯片,通过拉近存储单元与计算单元的距离、增加带宽,来降低数据搬运的代价,缓解由于数据搬运产生的瓶颈。未来,达摩院会进一步攻克存内计算技术。在应用方面,我们会和阿里内部业务紧密合作,未来逐步针对内部AI应用场景适配优化。

编辑:芯智讯-浪客剑

注:以上照片均为芯智讯独家拍摄,如需引用,请先获授权,谢谢!