11月8日消息,据日经亚洲评论报道,英特尔CEO帕特·基辛格(Pat Gelsinger)于 7日在中国台北“Intel Innovation Day”论坛指出,Intel 18A已研发完成,即将于2024年一季度进入测试生产阶段。

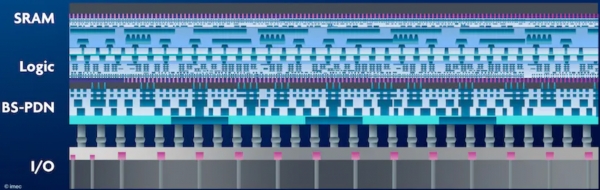

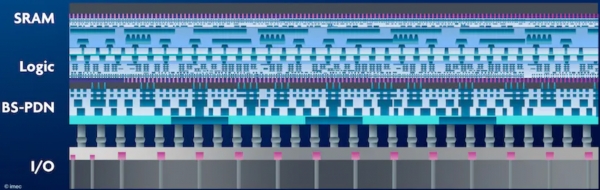

8月12日消息,台积电、三星、英特尔等晶圆制造大厂都在积极布局背面供电网络技术(BSPDN),并将导入尖端的逻辑制程的开发蓝图。据韩国媒体 The Elec 报道,继英特尔公布了其命名为“PowerVia”的背面供电技术将导入Intel 20A制程工艺之后,三星电子在此前日本VLSI研讨会上也公布了其背面供电技术的研究结果,也将用于其2nm制程工艺。

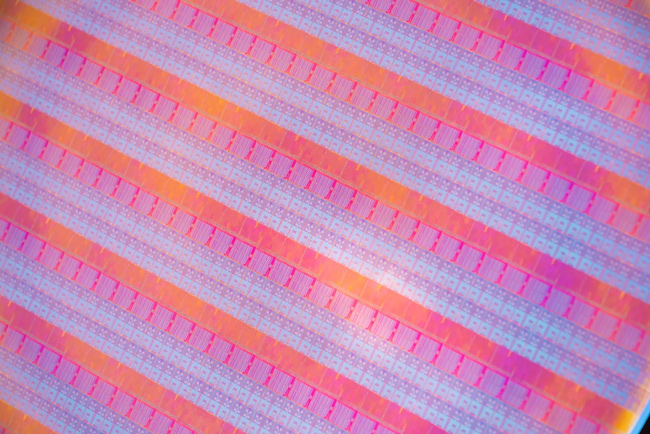

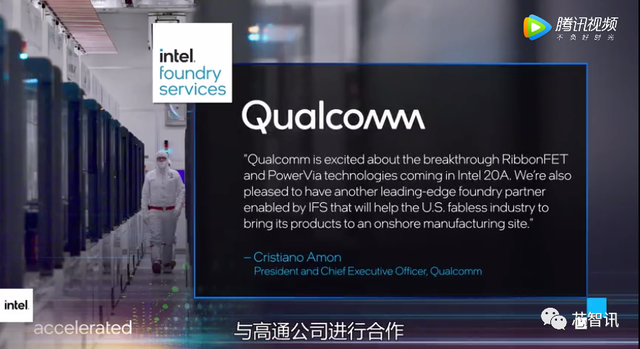

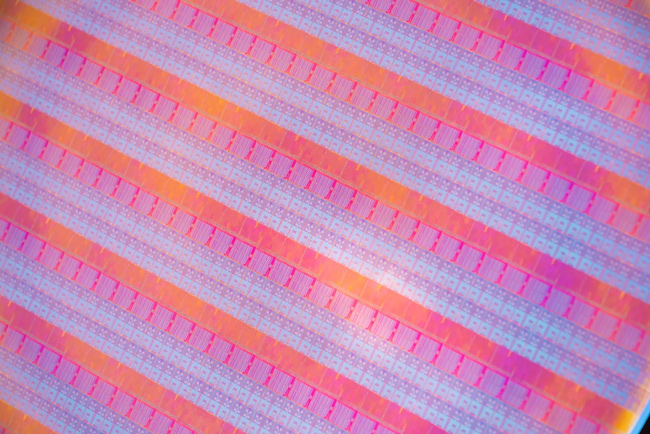

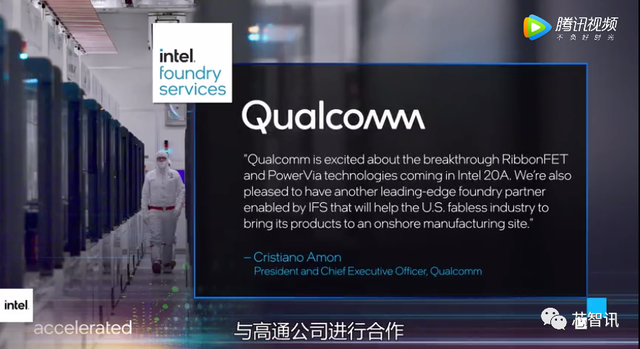

8月7日消息,处理器大厂英特尔日前介绍了其PowerVia背面供电技术,并指出Intel 20A将是旗下首个采用PowerVia背面供电技术及RibbonFET全环绕栅极晶体管技术的节点制程,预计将于2024年上半年达到生产准备就绪的阶段,将应用于未来量产消费性的ARL处理器平台,而目前正在晶圆厂启动First Stepping的前期阶段。

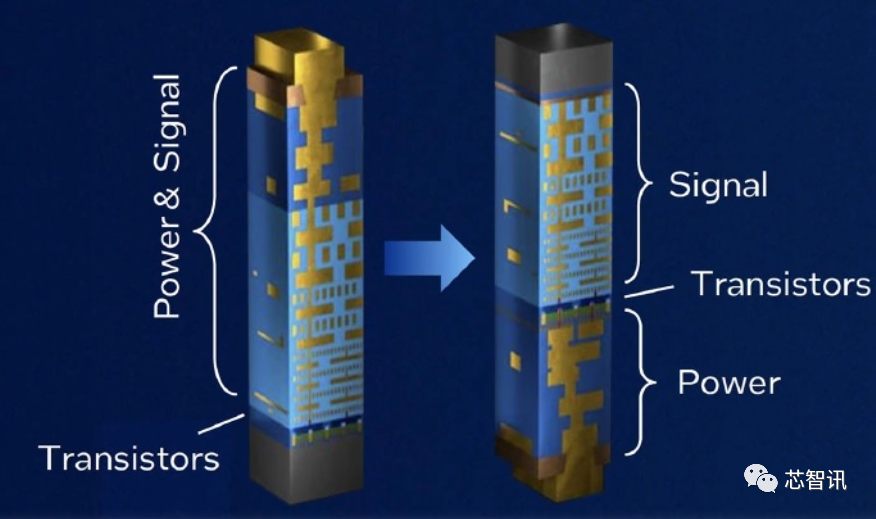

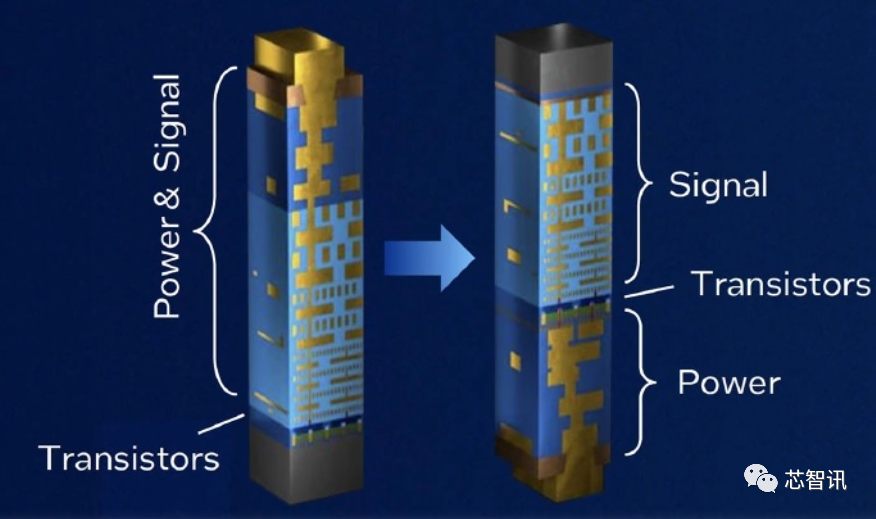

英特尔宣布在业内率先在产品级测试芯片上实现背面供电(backside power delivery)技术,满足迈向下一个计算时代的性能需求。作为英特尔业界领先的背面供电解决方案,PowerVia将于2024年上半年在Intel 20A制程节点上推出。通过将电源线移至晶圆背面,PowerVia解决了芯片单位面积微缩中日益严重的互连瓶颈问题。

2021年7月27日,英特尔CEO帕特·基辛格在“英特尔加速创新:制程工艺和封装技术线上发布会”上发表演讲。在这次线上发布会中,英特尔首次公布了未来数年的制程工艺和封装技术路线图,并对英特尔的工艺节点进行了重新命名。同时发布了全新的晶体管架构RibbonFET 和背面电能传输网络PowerVia,以及全新的Foveros Omni和Foveros Direct封装技术。