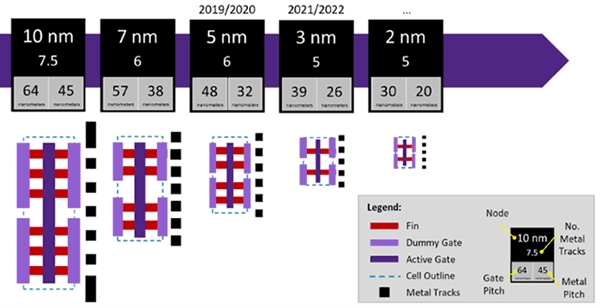

可以说在过去几十年,半导体产业在摩尔定律的推动下持续高速发展。但随着晶体管缩放尺寸逐渐逼近物理极限,半导体工艺制程的推进也越来越困难,“摩尔定律”已死的说法被越来越多的人认同。目前台积电、三星、英特尔等少数的尖端制程制造商,也只能依靠着越来越昂贵的EUV光刻机在艰难的推动半导体制程微缩,但是这依旧面临着非常多的工艺上的挑战以及成本难题。对此,科技界也希望寻找一些新的技术路径来改变目前的半导体制造困境,比如定向自组装(DSA)技术。

半导体技术的未来通常是通过光刻设备的镜头来看待的,尽管几乎永远存在着极具挑战性的技术问题,但光刻设备仍能为未来的工艺节点提供更好的分辨率。

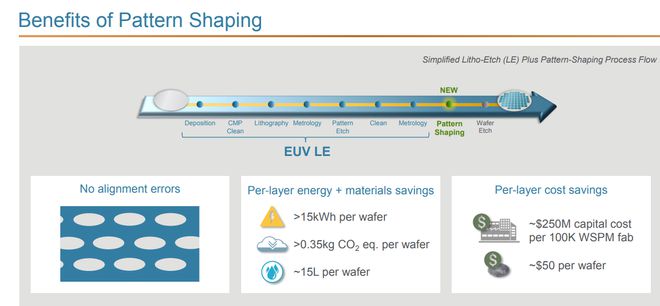

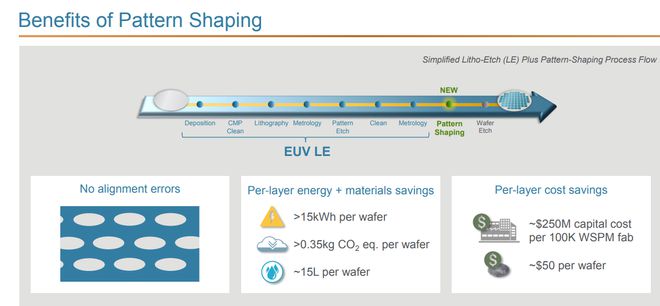

3月6日消息,半导体设备大厂应用材料 (Applied Materials)近日发布了一项突破性的图案化(patterning)技术,可协助芯片制造商以更少的EUV光刻步骤生产更高性能的晶体管和互联布线(interconnect wiring),进而降低先进芯片的制造成本、复杂性和环境影响性。

12月15日消息,据韩国媒体BusinessKorea报导,韩国本土的半导体和显示材料开发商——石墨烯实验室 (Graphene Lab) 开发出了基于石墨烯制造的EUV光罩保护膜 (Pellicle) ,有望显著提高ASML的极紫外光 (EUV) 系统生产芯片的良率。

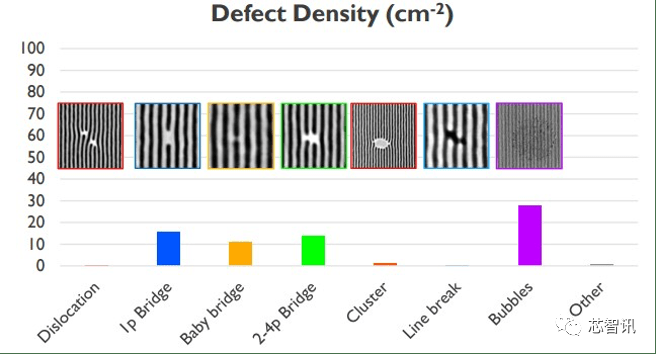

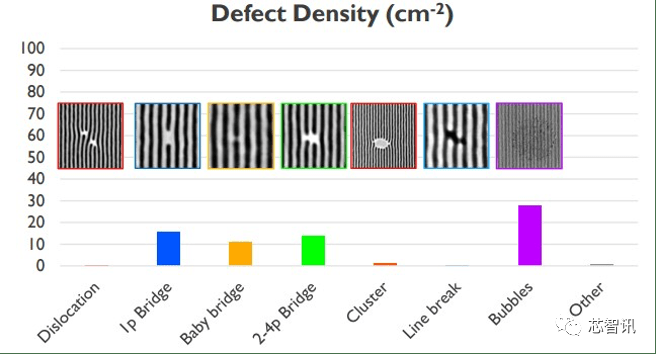

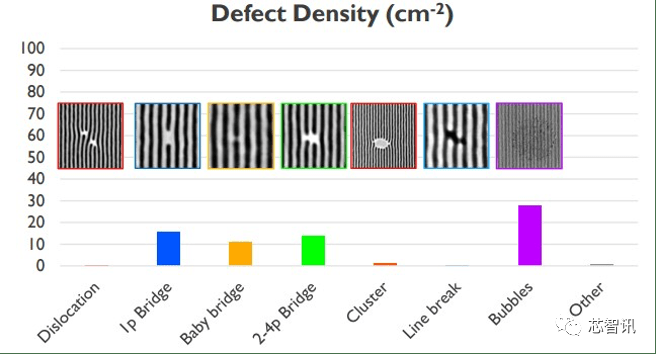

几家供应商正在推出下一代检测系统和软件,以定位极紫外(EUV)光刻机工艺引起的芯片缺陷问题。每种缺陷检测技术都涉及到各种权衡,但由于EUV引起的随机缺陷最终会影响芯片的性能,在晶圆厂里使用一项或多项检测技术是非常必要的。

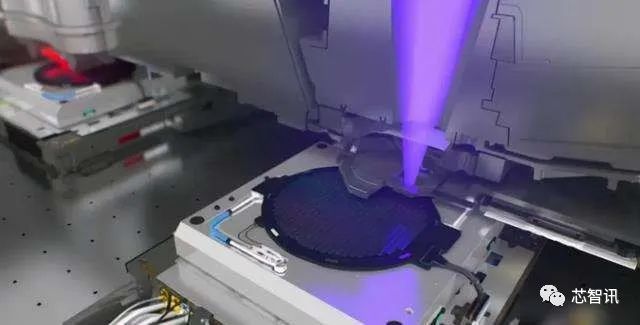

EUV 微影技术采用锡的电浆来产生波长为13.5 奈米的光源,以及用钼矽多层反射薄膜来把光传递到晶片上。不同于一般的紫外光微影技术,EUV 微影技术得在低真空中运作,技术难度更高。

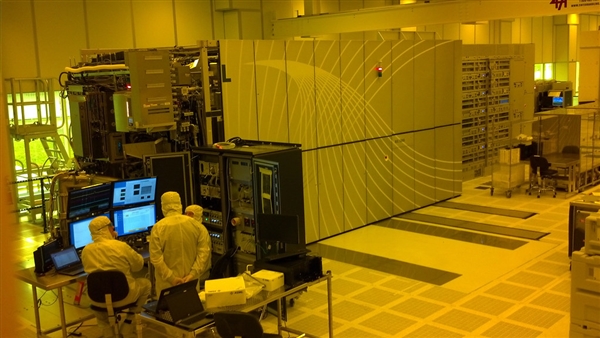

在半导体工艺进入7nm之后,EUV光刻机就成为兵家必备大杀器了,全球也只有ASML公司能生产,单价达到10亿人民币一台。不过在今年的EUV专利申请量上,蔡司排名第一,三星也超过了ASML。

去年11月,国际空间站的宇航员利用来自Astrileux的有效载荷,在国际空间站的外部平台上进行了光刻实验。实验围绕Astrileux的新EUV光学镀膜技术进行,目的是确定是否有可能使用Astrileux的EUV涂层捕获太阳EUV辐射。这些材料构成了波长为13.5nm的EUV光刻工具的光学器件和反射镜的基础。

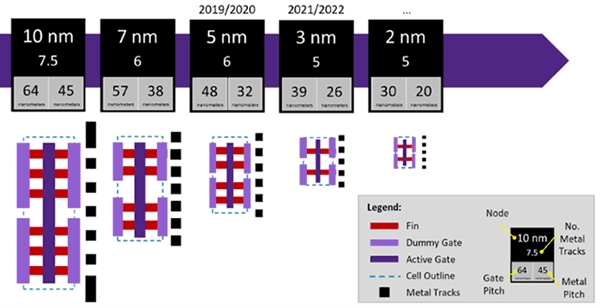

今年4月初,晶圆代龙头大厂台积电宣布,其5nm制程已正式进入试产阶段,并已在开放创新平台下推出完整的5nm设计架构。现在,台积电官方又宣布,正式启动2nm工艺的研发,工厂设置在位于台湾新竹的南方科技园,预计2024年投入生产。

今天,IBM宣布,将选用三星7nm EUV代工其Power11处理器,后者将用于蓝色巨人的Power系统、IBM Z、LinuxOne、高性能计算以及云服务解决方案中。

在芯片代工领域,如果说台积电、英特尔、三星属于第一梯队,那么格罗方德(GlobalFoundries)可能只能算是在第二梯队。而为了能够加速追赶第一梯队的厂商,2016年9月,格罗方德就宣布将跳过10nm制程,直接往7nm发展。

GlobalFoundries首席技术官Gary Patton近日在上海举行的一次技术会议上披露,GF EUV极紫外光刻技术的良品率已经提高到65%,公司将按计划推进EUV的商用和普及。