2月1日消息,晶圆代工大厂联电与EDA大厂Cadence于今日共同宣布,以Cadence Integrity 3D-IC 平台为核心的3D-IC 参考流程,已通过联电芯片堆叠技术认证,助力产业加快上市时间。

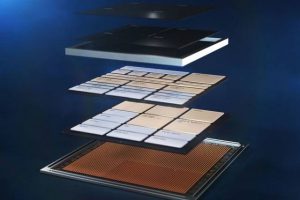

联电指出,旗下的混合键合解决方案已准备就绪,可整合广泛、跨制程的技术,支持边缘人工智能(AI)、影像处理和无线通讯等终端应用的开发。双方此次在晶圆对晶圆堆叠技术上的合作,采用联电40 奈米低功耗(40LP) 制程,以Cadence Integrity 3D-IC 平台验证了该设计流程中的关键3D-IC 功能,包括系统规划和智能凸块(bump) 的创建。Cadence 的Integrity 3D-IC 平台为业界首创的全面3D-IC 解决方案,可将系统规划、晶片与封装实现以及系统分析整合在单一平台上。

联电元件技术开发及设计支持副总经理郑子铭表示,过去一年,联电的客户在不牺牲设计面积或增加成本的情况下,寻求设计效能的提升方法,让业界对3D-IC 解决方案的兴趣大为提升。成本效益和设计可靠度的提升是联电混合键合技术的两大主轴,同时也是此次与Cadence 合作所创造的成果与优势,未来将可让共同客户享受3D 设计架构所带来的优势,同时大幅减省设计整合所需时间。

Cadence数字与签核事业群研发副总裁Don Chan 也强调,随着物联网、人工智能和5G 应用的设计复杂性不断增加,晶圆对晶圆堆叠技术的自动化对芯片设计工程师来说日益重要。Cadence 3D-IC 设计流程及Integrity 3D-IC 平台已经最佳化,结合联电的混合键合技术,可为客户提供全面的设计、验证和实现解决方案,让客户能自信地创建和验证创新的3D-IC 设计,同时加快上市时间。

此参考流程以Cadence Integrity 3D-IC 平台为核心,建立在高容量、多技术分层的资料库上。该平台可针对完整3D 设计专案,将设计规划、实现和系统分析,统整在一个管理平台中。在设计初期,即可针对3D 堆叠中的多个小芯片一并进行热完整性、功耗和静态时序设计和分析。参考流程还支持系统层级、针对连接精确度的布局验证(LVS) 检查、针对覆盖占比和对齐度检查的电气规则检查(ERC),以及针对3D 堆叠芯片设计结构中热分布的热分析。

编辑:芯智讯-林子