为应对人工智能、物联网、5G、智能汽车等新兴科技所迎来的海量数据分析需求,近年来各国政府及国际知名大厂皆积极地投入大量资源,加速开发兼具提升运算速度以及降低耗能的下世代记忆体。而新兴记忆体技术选项中,当属“铁电记忆体”最被看好,其原理、技术挑战与未来机会为何?(本文出自国立清华大学工程与系统科学系巫勇贤教授,于闳康科技“科技新航道” 合作专栏,介绍“铁电记忆体的原理、挑战与展望”文稿。)

Memory-Centric 晶片发展的必要性

数据是当今数位经济最重要的资源,根据估计,由于手持式装置的普及与物联网(IOT)的发展,每天会有超过2.5 quintillion (10 18 ) bytes 的数据被产生,且这个数据产生的速度仍不断攀升。

如此巨量的资料也意谓着在处理上需要耗费大量的运算资源,尤其是目前建构在冯诺伊曼(von Neumann)架构的计算机在进行运算时,数据资料必须在运算单元(CPU或GPU )与记忆体间进行反覆的传输,不仅限制整体效率与计算时间,无法满足实际即时应用情境,更造成大量的能量消耗,这是因为反覆资料传输限制了效能提升,造成了所谓的Memory Wall。

迈入整合大数据(big data )与人工智慧(AI )的世代,为了克服Memory Wall的限制并提升运算效能,让记忆体更紧密结合运算资源的Memory-Centric晶片近年来受到相当大的关注。

所谓的Memory-Centric 晶片主要是指Near-Memory Computing 与In-Memory Computing 两种整合记忆体与运算的技术。Near-Memory Computing是透过先进封装技术以晶片层级整合(die-level integration)将运算晶片与记忆体晶片整合在一起,或将运算电路与记忆体电路以积层型(monolithic)的制程方式,进行垂直式元件层级整合(device-level integration),目标均是让资料运算单元与记忆储存单元两者更为接近,减少传输的距离。

克服冯诺伊曼架构限制的In-Memory Computing

至于In-Memory Computing则是直接利用记忆体处理深度学习(deep learning)中人工神经网路,包括深度神经网路(Deep Neural Network, DNN)、卷积神经网路(Convolutional Deep Neural Network, CNN)等多项神经网路的运算任务,无须将资料在运算单元与记忆体间反覆传输,可克服冯诺伊曼架构的限制,在运算效能上获得显著的提升。

更进一步地,可以利用记忆体实现神经系统的突触(synapse)、轴突(axon)与神经元(neuron)行为,应用于新一代的脉冲神经网路(Spiking Neural Network, SNN),仿照人类大脑运算与认知模式,将运算与记忆都在同一个地方执行,也称为神经形态运算(neuromorphic computing),是未来运算架构的典范[1]。

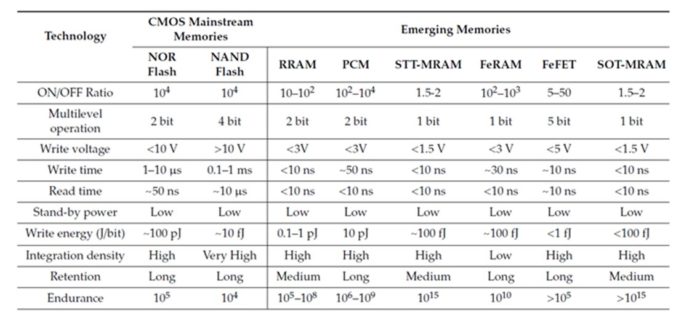

In-Memory Computing架构中的核心是兼具运算与储存功能的记忆体元件,传统的NOR/NAND 快闪记忆体(Flash)与大部分新兴记忆体(emerging memory)如电阻式记忆体(Resistive RAM, RRAM)、相变化记忆体(Phase Change Memory, PCM)、磁阻式记忆体(Magnetoresistive RAM, MRAM)与铁电记忆体(ferroelectric memory)均具备实现In-Memory Computing 或neuromorphic computing 的能力。相对于其他种类的新型态记忆体,铁电记忆体由于在制程相容性与元件效能方面极具有竞争优势,近年来引起学界与业界的高度瞩目。

铁电材料的前世今生

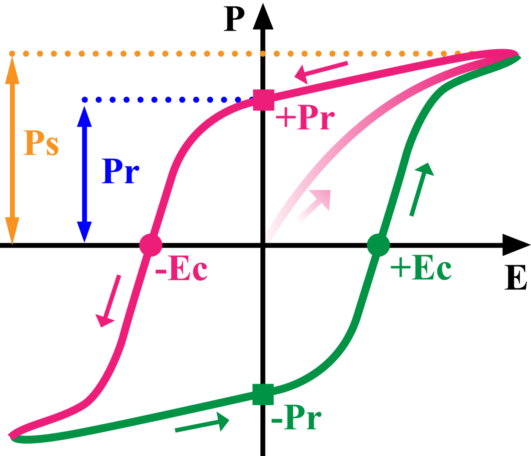

铁电材料(ferroelectric materials )是一种具有自发极化,亦即在无电场存在的情况下,晶胞(unit cell)结构中使正/负电荷中心分离形成电偶极(dipole)的材料。铁电材料中,自发极化的电偶极方向并不一致,但在某一个特定区域内,各晶胞的自发极化方向相同,这个特定区域称为铁电畴(ferroelectric domains)。

铁电畴的极化方向和强度各不相同,在整个材料中随机分布,相互抵消后,整体的铁电料并没有极化的现象。对铁电材料施加电场后,每个铁电畴的极化方向会趋于一致,并达到饱和极化值(saturation polarization, Ps)。

当电场超过正的矫顽电场(positive coercive field, +Ec)或低于负的矫顽电场(negative coercive field, -Ec)即可改变铁电材料之电偶极方向。当外加电场移除后,铁电材料内仍会有剩余的极化量存在(remanent polarization, P r),故非常适合应用于非挥发记忆体元件(non-volatile memory)。

▲图一铁电层电场与极化量示意图

铁电材料并不含铁元素的成分,会这样命名是来自前述电偶极随外加电场变化的行为与铁磁材料(ferromagnetic materials )之铁磁畴(ferromagnetic domains )随外部磁场改变磁化量的特性类似所致。

铁电材料自1920 年罗歇尔盐(Rochelle Salt)被提出至今已满100 年,而后长达半世纪的时间,科学家们着重于研究钙钛矿(perovskite)结构的传统铁电材料,如BaTiO 3(BTO)与Pb[Zr x Ti 1-x ]O 3(PZT)等铁电材料,尤其PZT 更已应用于商业化的铁电记忆体。不过PZT 铁电材质并不相容于目前的积体电路制程,例如Pb/O 2 扩散现象、特性易受H 2 影响、不易于原子层沉积(atomic layer deposition)制程整合等问题,提高了量产化的障碍[2]。

此外,钙钛矿薄膜的铁电性(ferroelectricity)在厚度低于某个临界值后即会急遽劣化,第一原理计算预估6 个单晶格(unit cell)为钛矿铁电材料之临界值[3],也就是厚度微缩有其限制,这使得记忆体尺寸无法缩小,导致记忆体密度无法有效提高,因此以PZT 为主的铁电记忆体仅在半导体记忆体市场占有极小的比例。

适合先进制程、无微缩临界值,铁电材料备受瞩目

2011 年首次发现以Si 掺杂的HfO 2具有铁电特性后[4],这种具氟石(fluorite)结构的氧化物如掺杂的HfO 2或HfO 2/ ZrO 2之固溶体(solid solution)引起了学界与业界高度的瞩目。欧盟在这方面尤其积极,其中Horizon 2020 计画所支持的3εFERRO(Energy Efficient Embedded Non-volatile Memory ?& Logic based on Ferroelectric Hf(Zr)O 2)就是一个显著的例子。

相较于传统的钙钛矿铁电材料,铁电层主要优点不仅在于材料与制程完全相容于现有先进制程技术,更重要的是,在10 nm等级的厚度下HfO 2为基础的铁电层仍保有铁电性。

2020 年的研究更发现,基于HfO 2的铁电层厚度微缩至1 nm,自发极化与可改变极化方向之现象仍可持续出现。这意谓着具有铁电性之HfO 2薄膜并无微缩的临界值,微缩厚度甚至可强化极化形变(polar distortion),对于以极化驱动之记忆体元件有相当优异的发展优势[3]。

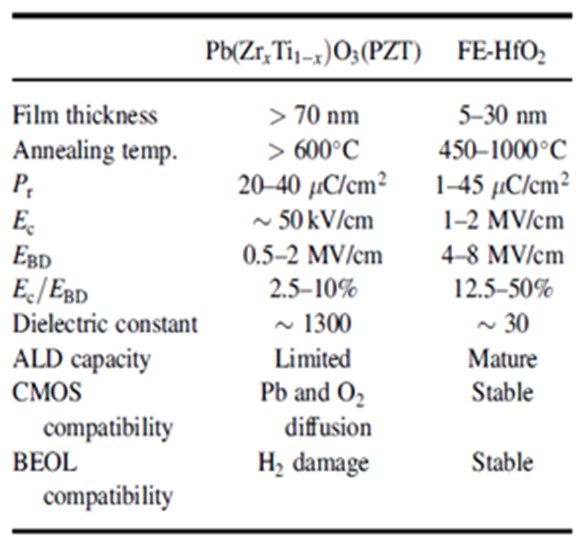

图二是PZT 与HfO 2铁电层的特性差异比较[2],一个值得注意的数值是Ec,两者存在着高达20-40 倍的显著差异,这与铁电记忆体的效能与可靠度有高度的关联性。

▲图二钙钛矿(PZT)与基于HfO 2铁电材料特性比较表[2]

HfO 2铁电材料形成机制

为了持续开发高速、低耗能且高可靠度的铁电记忆体,深入探究HfO 2铁电层的形成机制是相当必要的。事实上,基于HfO 2的氧化层具有铁电性是材料科学上极为重要的发现,其原因在于热力学稳定下的HfO 2不论从实验或是计算的平衡相图(equilibrium phase diagram)均显示其为不具铁电性的中心对称(centrosymmetric)结构。

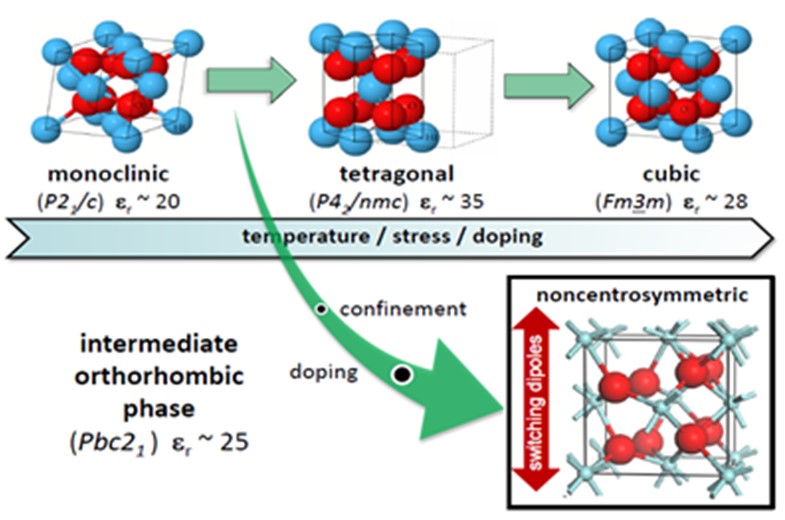

在室温常压下,HfO 2最稳定的晶相是monoclinic 晶相(P2 1 /c , m-phase),升温后则转换至tetragonal 晶相(P4 2 /nmc , t-phase)或cubic 晶相(Fm3m , c-phase),而升压时形成具顺电性(paraelectric)/非极化(non-polar)之orthorhombic 晶相(P bca , P mna),不过这些晶相都不具备铁电性。由实验与理论计算得知,具铁电性之HfO 2 是结晶成非中心对称(non-centrosymmetric)/极化(polar)之orthorhombic 晶相(Pca2 1 , o-phase)[5],施加电场时,HfO 2 中的氧原子会受到电场影响而发生位移也就是所谓的极化[3]。

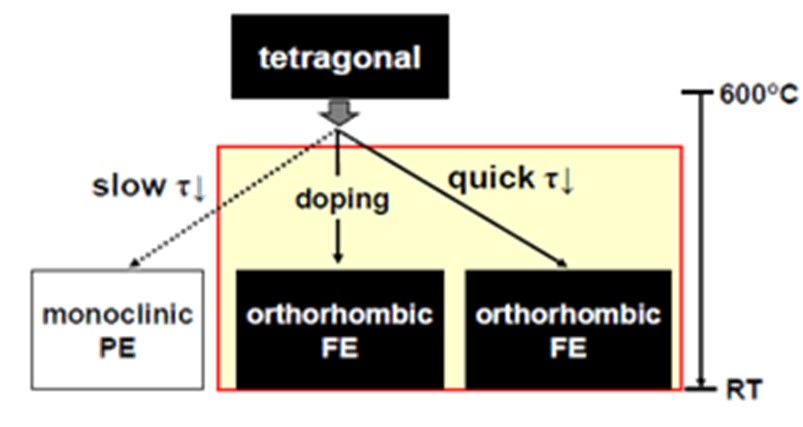

HfO 2 如何形成铁电性所需的亚稳定态(metastable)晶相o-phase 一直是热门的研究议题。HfO 2 由亚稳定态晶相(如t-phase)经相转变(phase transformation)形成稳定态晶相m-phase 后,就无法再转变为其他亚稳定态晶相,这是属于一种不可逆的过程(irreversible process)。一般认为亚稳定态晶相o-phase 应该是由其他亚稳定态t-phase 转变而来的,其原因在于两者的结构相似性,而施加非等向性应力(anisotropic stress)是发生此转变的关键之一。常见的HfO 2铁电层制程如掺杂(doping)、表面能效应(surface energy effect)、岛状物聚结(island coalescence)、热膨胀不匹配(thermal expansion mismatch)、金属覆盖层(metal capping layer)以及氧空缺(oxygen vacancies)形成都与非等向性应力有关[6]。图三为HfO 2薄膜经不同制程下所显示的各晶相演进与晶体结构[7]。

▲图三HfO 2 薄膜经不同制程下所显示的各晶相演进与晶体结构[7]

热制程的条件在铁电薄膜的形成过程相当关键,温度必须够高方能使薄膜结晶,但过高的温度又可能形成不可逆的m-phase 。

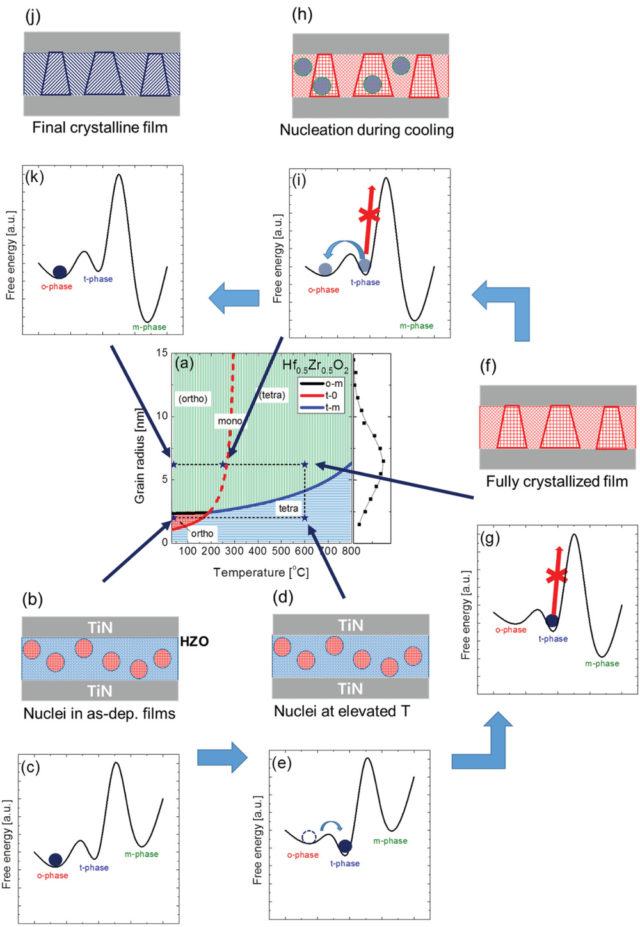

由动力学模型亦可说明HfO 2 薄膜形成o-phase 的机制,如图四所示[8],以掺杂Zr 的HfO 2 薄膜(Hf 0.5 Zr 0.5 O 2,HZO)为例,回火制程各阶段晶相的变化可分为四个阶段:

初始阶段:刚沉积的fluorite 结构薄膜具有极微小(约2 nm 半径)的成核点(nuclei),且很有可能以o-phase 的微晶形式(nanocrystallities)存在。

升温阶段: t-phase 因为其熵值(entropy)较o-phase/-phase 低,造成其free energy 下降,因此这个阶段薄膜的稳定相将由o-phase 转成t-phase。

持温阶段: m-phase 的free energy 会降低,根据热力学的理论,薄膜应该倾向形成m-phase。不过由于t-phase 与m-phase 存在着高达250 meV/formula unit(fu)的能障,故薄膜在此阶段仍维持t-phase,然而更高的回火温度与更长的回火时间将可能使系统具备超过此能障的能量,使薄膜形成m-phase。

降温阶段:由于t-phase 与o-phase 间的能障仅30 meV/fu,薄膜非常有机会形成第二稳定态o-phase 而非最稳定态m-phase。

欲使薄膜尽可能形成o-phase,降低o-phase 之free energy 是必要的,如图五所示,提高回火制程中的降温速率(τ) 有益于增加薄膜中o-phase 的比例[9]。近期的研究亦报导以水进行快速冷却(fast quench)可使HfO 2 铁电薄膜之Pr 与Ec 分别达到50 μC/cm² 与4 .75 MV/cm,远超过一般快速热退火制程所呈现的结果[10]。

▲图四掺杂Zr 之HfO 2 薄膜于回火过程相图[8]

▲图五降温速率与薄膜晶相关系图[9]

铁电记忆体种类及其运作原理

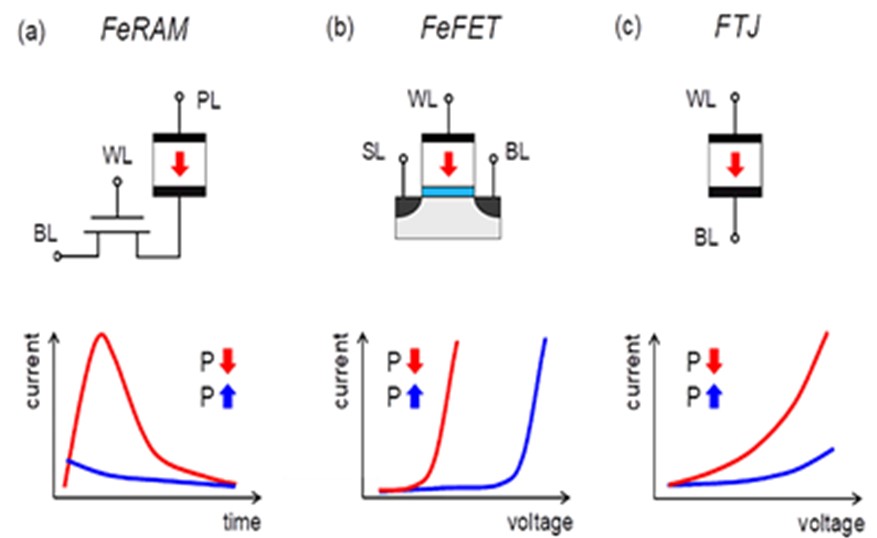

铁电材料应用于记忆体主要分为三种记忆胞(memory cell)结构,如图六所示,包括(a)一个电晶体与一个铁电电容所组成的ferroelectric RAM(FeRAM)、(b)单一电晶体形式的ferroelectric FET (FeFET)与(c)上/下电极包覆铁电薄膜的ferroelectric tunnel junction(FTJ)[11]。

▲图六不同结构之铁电记忆体与对应读取电流示意图[11]

(a)FeRAM 记忆体

早在1940~1950 年代BTO 与PZT 等钙钛矿结构之铁电层被陆续提出,其中1952 年MIT 的硕士生首先在其论文提出以BTO 的铁电电容作为资料储存的元件,可以被视为FeRAM 的雏型。如图六(a)所示,FeRAM 记忆胞是由一个电晶体与一个铁电电容所组成,与现有主流的动态随机存取记忆体(DRAM)记忆胞结构类似,其中铁电电容是由金属上电极/铁电材料/金属下电极所构成。此记忆胞结构中,铁电电容的下电极电压透过电晶体由位元线(bit line, BL)所控制,而上电极电压则由金属板线(plate line, PL)所决定,藉由上电极/下电极的电压极性与差异即可改变铁电电容内电偶极的方向。

假设电偶极方向朝上是逻辑「1」,朝下是逻辑「0」,欲写入资料逻辑「0」资料至铁电电容,可在电晶体开启的情况下,于BL 与PL 分别施加0 V 与高电压(如Vcc)。反之,则可写入逻辑「1」资料。欲读取资料,则可以在BL 与PL 两处分别施加0 V 与Vcc。若储存于铁电电容的资料是逻辑「1」,则电偶极会转变方向而成为逻辑「0」并产生转换电流(dipole switching current),继而对BL 充电,使BL 电压提高。反之,若储存于铁电电容的资料是逻辑「0」,则电偶极方向保持不变,BL 电压几乎没有改变。

藉由量测BL 电压的高低数值即可判断铁电电容储存的资料是逻辑「1」还是逻辑「0」。然而不论原来储存的资料为何,一旦经过读取的过程,所有的资料都会转换成逻辑「0」,是一种明显的破坏性读取(destructive reading),因此必须在读取资料后再写入正确的资料。

基于PZT 铁电材料之商用型FeRAM 记忆体写入资料的速度约在数十奈秒等级(ns),具有长达10 年的资料(极化)保存能力(retention),且反覆操作耐受力(endurance)可高达10 15 次。值得注意的是铁电电容的资料保存能力与去极化电场(depolarization field)的大小有密切关系。理想的情况下,铁电层极化时,电极上所诱发电荷Q 可以完全补偿(compensate)铁电层内的极化量P,在此情况下,铁电层内部的电场为零。

然而实际的电极并非理想导体,因而导致Q 与P 之间不平衡并造成铁电层内的电场,即所谓的去极化电场。去极化电场越大则会使铁电层内的极化程度随时间衰减,极化保存能力劣化。去极化电场是无可避免的,所幸FeRAM 记忆体的铁电电容是以金属作为电极,去极化电场较小,因此仍能达成优异的资料保存能力。

若以HfO 2 铁电层制作FeRAM,与PZT 相较之下,其较高的Ec 也更能抵抗去极化电场的影响。与DRAM 相较之下,FeRAM 是仰赖铁电层的电偶极方向来储存资料,而非DRAM 以电荷储存资料,没有电荷流失的问题,因此无须进行周期性的资料更新(refresh)。由于资料的储存与电荷无关,当面对辐射所引发的电流及可能的资料破坏具有更高的免疫力,因此也常应用于太空任务与核子医学仪器所需的电子设备。另外,FeRAM 是属于非挥发性记忆体,与DRAM 挥发性记忆体的特性有相当大的属性差异。

经过多年发展,FeRAM 记忆体市场也发生了相当大的变化,1992 年Ramtron 公司开始销售商用型FeRAM,2011 年Texas Instruments 发表首款以FeRAM 为基础的微处理器,到了2012 年Cypress 公司取得了Ramtron 公司,而2020 年Infineon 公司又购买了Cypress 公司,自此FeRAM 也成为Infineon 公司应用于车用电子的记忆体之一,目前Infineon 公司最大容量的FeRAM 晶片为16 Mbit,且仍以PZT 作为铁电材料。

(b)FeFET 记忆体

1950 年代后期以BTO 铁电层发展出了第一个FeFET 记忆体,时至今日,FeFET 记忆体之记忆胞是以单一电晶体架构为主,如图六(b)所示,制程上仅需将制作于MOSFET 电晶体的闸极介电层改以铁电材质取代即可。

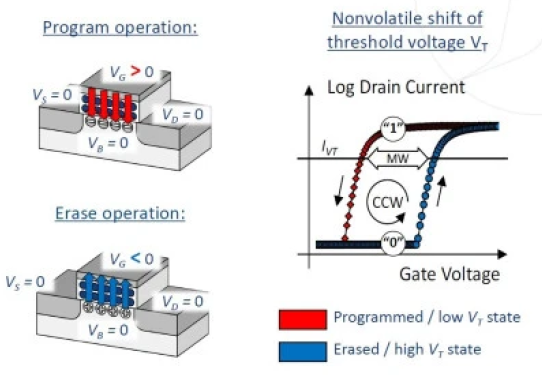

▲图七FeFET 记忆体操作机制示意图[12]

对于n 型通道之FeFET 记忆体而言,如图七所示,欲写入资料可在闸极施加高于+Ec 或低于-Ec 的电场。施加高于+Ec 电场可使电偶极方向朝下,在通道形成强反转(inversion)状态,此时元件呈现低临界电压(threshold voltage, Vt)状态,或称逻辑「1」状态。反之,施加低于-Ec 的电场,则使元件呈现高临界电压状态,或称逻辑「0」状态。

逻辑「1」或「0」所对应的Vt 差异称为记忆视窗(memory window, MW),越大的记忆视窗意谓着越容易区分逻辑「1」或「0」的差异[12]。当一个记忆胞仅储存2 种Vt 状态(如逻辑「1」与「0」)即表示可以存放1 个位元(bit)的资料,若记忆视窗增加,则代表在此范围内可以容许其他不同的状态,能够区分4 种Vt 状态则表示可以存放2 个位元(bit),目前已有文献报导FeFET 记忆体可以实现存放3 个位元(bit)[13]。

FeFET 记忆体可藉由不同的闸极电压调整电偶极的转向程度,继而控制通道内的载子数量,达到实现不同Vt 的目标。这种以单一记忆胞即可储存2 个或3 个位元的情况类似NAND Flash 记忆体技术的多层式储存(Multi Level Cell, MLC)与三层式储存(Triple Level Cell, TLC)的概念,可以降低至制造成本并大幅提升记忆体密度。欲实现单一记忆胞多位元储存的目标,提高记忆窗是必要的条件之一。

▲图八FeFET 记忆体的记忆视窗

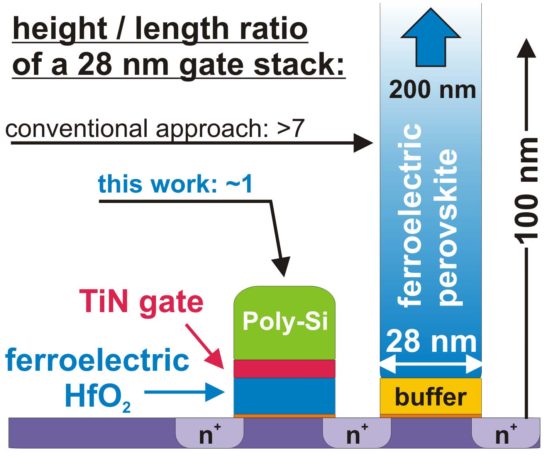

理论上FeFET 记忆体所能够达到的记忆视窗约可表示成2t f ×E C,其中t f 为铁电层厚度,E C 则为矫顽电场。如图八所示,由于传统钙态矿铁电材料如PZT 之Ec 较小,欲实现较大的记忆视窗,势必要沉积较厚的铁电层厚度,这也是PZT 材料应用于FeFET 记忆体无法微缩的瓶颈之一,反观HfO 2 铁电材料,较大的Ec 则可允许以较薄的厚度实现所需的记忆视窗,对于FeFET 记忆体的发展有相当大的助益。

FeFET 记忆体的效能评估除了记忆视窗外,操作速度与资料保存能力也相当重要。对基于HfO 2 铁电层之FeFET 记忆体而言,其写入资料的速度大约在10 ns 的等级且拥有优异的资料保存能力。值得注意的是FeFET 记忆体的铁电层是沉积于半导体之上,而非FeRAM 的铁电电容其铁电层是沉积于金属之上,因此前述的去极化电场在FeFET 记忆体会更加明显。所幸HfO 2 铁电层之Ec 约为1-2 MV/cm,可以有效抵抗去极化电场的反向效应,故仍能保有极为优异的资料保存能力。

(c)FTJ 记忆体

FTJ 记忆体的结构相对简单,如图六(c)所示,为铁电层被上/下电极所包覆的三明治结构。藉由铁电层极化量方向可调变能障高度(barrier height),由于穿隧电流与能障高度之间呈指数函数关系,因此可进而改变穿隧电流大小并引发穿隧电阻(tunneling electroresistance, TER),形成高电阻与低电阻间转换。

目前大多数报导的FTJ 记忆体其操作电压可在4V 以下,操作速度介于10-100 ns 之间,具备低写入功耗与非破坏性读取等优点,明显优于传统的Flash。另外,FTJ 记忆体高/低电阻比例(TER ratio)或称ON/OFF比例大概介于10-100 之间。通常提高增加铁电层厚度有助于提高TER ratio,不过这会使得导通电流与读取电流下降,读取时间增加。另一种较为可行的方案则是采用包括铁电层与介面层在内的双层结构,使电偶极切换与穿隧电流发生在不同薄膜。

FTJ 记忆体目前仍然处在非常初期的开发阶段,对于阵列结构下的潜泄电流(sneak current)的抑制以及高/低电阻之统计分布相关分析仍有待进一步研究全。尽管FTJ 记忆体具有成为下世代记忆体的高度潜力,不过以现阶段而言,低电流密度限制了读取资料的速度,因此比较适合应用于In-Memory Computing 中的大量平行运算[11]。

总结来说,虽然早期的铁电记忆体发展大多是采用基于钙钛矿族的锆钛酸铅(PZT)来制作,碍于该材料本身的压电特性复杂及制程上保形沉积困难等限制,其产品应用仅局限于利基市场。而近年来随着半导体常见材料HfO 2被发现具有铁电相特性,且该材料的应用制程复杂度低、成本上更具优势,才终于为铁电记忆体推升另一波新的产业发展契机。

基于 HfO 2 之铁电记忆体其挑战与机会

基于HfO 2铁电层的FeRAM或是FeFET记忆体,尽管在功率消耗、操作速度、非挥发性与制程相容性等面向均极具有优势,然而在迈向半导体市场最大的挑战来自于反覆操作之endurance表现。

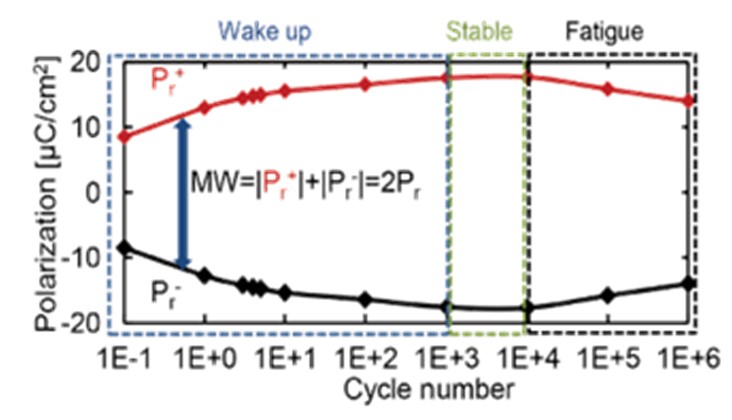

图九是典型FeRAM 记忆体其铁电电容元件(TiN/HfO 2 铁电层/TiN)之极化量与操作次数的关系图,图中可明显观察到极化量随操作次数增加而上升(唤醒效应,wake-up effect),而后渐渐劣化(疲乏效应,fatigue effect),铁电电容最终可操作的次数则由铁电层崩溃(breakdown)所限制[15-16]。

▲图九FeRAM 记忆体之反覆操作耐受力(endurance)[15]

wake-up 与fatigue 效应可能会造成了资料的错误判读,因此需要尽量抑制此效应。一般认为wake-up 是初始时将铁电畴壁钉扎(domain wall pinning)之氧空缺随着操作次数增加而获得能量并重新分布(redistribution),进而舒缓了钉扎现象或是介面处的铁电层晶相由t-phase 转变成o-phase 所致。

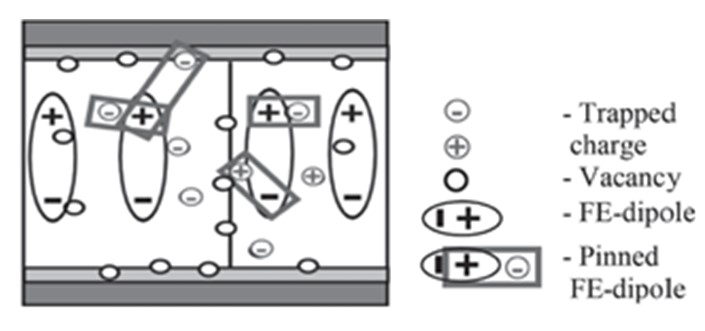

至于fatigue 则来自于反覆操作下于TiN电极/HfO 2 铁电层介面处TiOx 所产生的氧空缺并造成电荷捕获(charge trapping),如图十所示,这些被捕获的电荷可能形成新的电偶极并导致铁电畴壁钉扎的结果[15],而breakdown 也与持续地累积氧空缺的数量,形成永久漏电流路径有关[17]。

▲图十铁电层发生畴壁钉扎示意图[15]

抑制金属电极与HfO 2 铁电层之间可能的介面反应是减少氧空缺的关键[16],已有文献指出在金属电极沉积后,HfO 2 铁电层沉积前,透过适当的NH 3 电浆氮化处理可以有效抑制介面反应,使元件免于唤醒与疲乏效应[18]。另一方面,减缓breakdown 效应也是延长铁电记忆体操作次数的途径之一。

由图二的资讯可发现HfO 2 铁电层之Ec 较传统钙态矿铁电层增加数倍,虽然有益于抵抗去极化电场或是提高FeFET 记忆体之记忆视窗,但另一方面,HfO 2 铁电层之Ec 最高可达到崩溃电场(breakdown field、E BD)的50 %,反观PZT 之Ec/E BD 比值最高仅10 %,这项参数意谓着HfO 2 铁电层以较为接近崩溃的电场进行操作,因此可操作次数不如采用PZT 的铁电记忆体。

提升Endurance 是主要挑战

欲延长操作次数,降低HfO 2 铁电层之Ec 是可行的方案之一,文献上已有报导将Hf 0.5 Zr 0.5 O 2 铁电层掺入La 元素可以降低Ec,endurance 可达到10 11 次,这是大面积铁电电容(2000 μm 2)下所呈现最佳的endurance 表现[19]。掺杂Si 元素的HfO 2 也是能降低铁电层Ec 之制程,透过铁电电容面积微缩至28 μm 2,缺陷密度较能掌控的情况下,endurance 预期可达到10 12 次[20]。

另外,也有研究团队提出以具有印记效应(imprint effect,因内建电场导致+Ec/-Ec 不对称的现象)的反铁电(antiferroelectric)材料降低元件的操作电压,研究成果显示endurance 可超过10 10 次[18]。由于调控HfO 2 薄膜中掺杂Zr 的比例即可实现反铁电材料,同样相容于现有制程,是相当值得投入研究方向。若要将FeRAM 整合于随机存取记忆的应用,endurance 至少要达到10 15 次,因此仍有努力提升的空间。

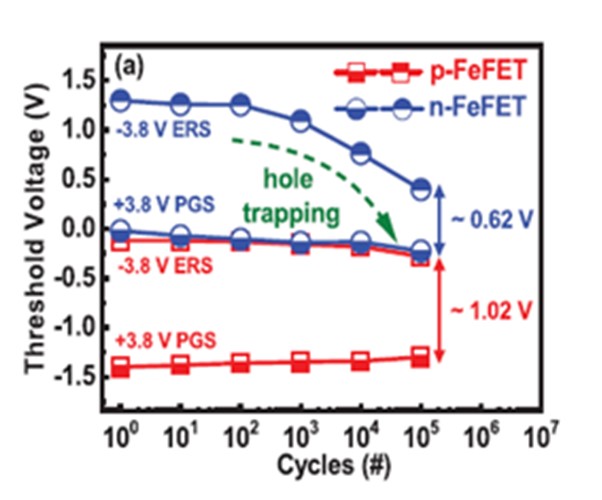

FeFET 记忆体的endurance 通常在10 5 ~10 9 次,与前述铁电电容元件的落差原因,来自于其HfO 2 铁电层与半导体接触时无可避免的介面反应,使得提升FeFET 记忆体之endurance 更具有挑战性。

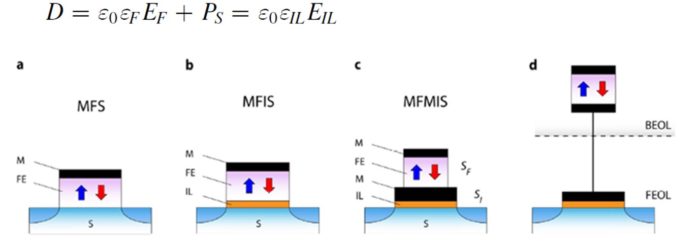

图十一显示了从制程与结构的角度提升endurance 的主要途径,如图十一(a)所示,以矽晶半导体基板为例,HfO 2 铁电层在回火的过程中会因为结晶成铁电晶相而使介电常数提高至25,并于HfO 2/Si 之间会产生介电常数3.9 的SiO x 介面层。根据电位移场(electric displacement field)须保持连续性的特性,铁电层电场(E F)与介面层电场(E IL)需满足以下关系式。

此关系式也意谓着铁电层的饱和极化值(Ps)越大反而会造 IL 承受更高的电场,不利于 endurance表现 [22]。以E F 约等于Ec(1 MV/cm)估算,当Ps 大于5 μC/cm² 时,E IL 将大于20 MV/cm,极化量越大,E IL 越大,也会越接近介面层崩溃的电场。因此FeFET 记忆体的endurance 通常不是由铁电层本身决定,而是被介面层特性所限制[19-21]。

▲图十一 不同氧化层堆叠结构之FeFET 记忆体示意图[22]

在不同闸极偏压的极性下,SiO x 介面层的高电场会导致电荷易于由闸极金属或矽通道注入,反覆操作下会发生介面陷阱产生(interfacial trap generation)或电荷捕获(charge trapping)效应,前者导致FeFET 记忆体元件之次临界摆幅(sub-Vt swing)劣化,而后者则会造成Vt 的偏移,两者均会使记忆视窗缩小,不利于元件持续操作[25]。如图十一(b)所示,为了减少电荷注入所造成的负面效应,成长高介电常数介面层,降低E IL 是可行的方式之一。

如图十二所示,导入介电常数达9 的AlON 介面层,由于EIL 降低,可以有效抑制电荷注入,因此可以在高电压(±5 V)、长时间脉冲(10 -4 s)操作下仍达到10 5 次的endurance 表现。

▲图十二 高介电常数AlON 介面层之TEM [26]

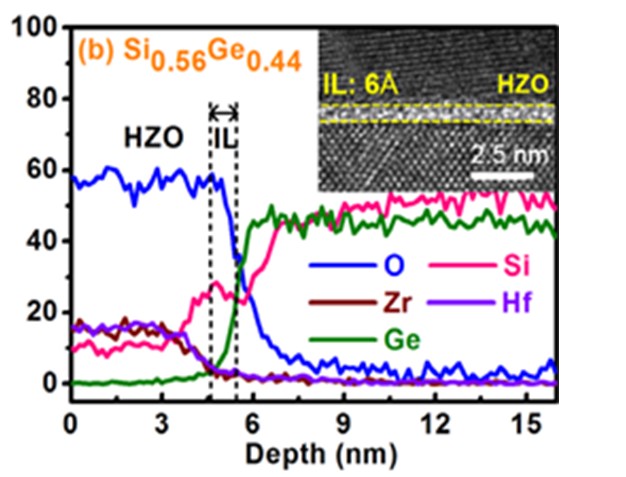

此外,由于铁电层电场提升,也可以使电偶极做更有效的转换,故也可以在±4 V 的电压操作下获得高达3.1 V 的记忆视窗[26]。文献上以SiNx 作为介面层也是类似的概念,结果显示在低电压(±3 V)、短时间脉冲(250 ns)操作下可达到相当出色的10 10 次endurance 表现[27]。如图十三所示,导入磊晶SiGe 通道也可以因为介面层品质改善而达到endurance 提升的效果[28]。

▲图十三 SiGe 基板上之铁电薄膜介面特性[28]

除此之外,有别于多数FeFET 记忆体以n 型通道为研究对象,如图十四所示,近期的研究发现p 型通道因为热电子(hot electrons)引发的电洞数量较为和缓,故呈现更为优异的endurance 表现[29]。

▲图十四FeFET 于不同通道种类下之endurance 特性表现[29]

铁电电容的新元件结构享有较为优异的endurance 表现,透过调整各层比例使大部分电压落在铁电层,减少介面层的压降,达成减缓电荷注入所造成的负面效应并提高记忆视窗,不仅可靠度表现可以提升,热制程也可以分别调整是此结构的优点。

另一方面,如图十一(c)所示,由于铁电电容元件享有较为优异的endurance 表现,在前述FeFET 记忆体的铁电层与介面层之间沉积金属形成金属/铁电层/金属/介面层/半导体的新元件结构,其中金属/铁电层/金属可视为铁电电容,故元件的endurance 表现可获得提升。此外,此结构上半部金属/铁电层/金属部分的面积(S F)与下半部金属/介面层/半导体部分的面积(S I)可分别调整其比例使得S I/S F 大于1,目的是藉由上半部电容值小于下半部电容值,使大部分电压落在铁电层,减少介面层的压降,达成减缓电荷注入所造成的负面效应并提高记忆视窗。

如图十一(d)所示,前述的记忆体结构可以进一步将上半部铁电电容元件与下半部电晶体元件分别在后段与前段制程完成,不仅可靠度表现可以提升,热制程也可以分别调整是此结构的优点[30]。不过铁电电容元件的下电极是类似浮动闸极(floating gate)角色,漏电流或反覆操作次数过多时可能使浮动闸极累积过多电荷而无法排除,导致发生过度屏蔽(over screen)铁电层极化的现象,使记忆体无法正常运作,故此结构在材料的选择与厚度上均需要谨慎的设计[22]。

铁电记忆体的展望

自HfO 2 铁电材料发现后,为FeRAM、FeFET 与FTJ 记忆体的发展开启了一个新的契机。众多顶尖团队经过10 年努力,整合了创新的材料、制程与结构,在FeRAM 与FeFET 记忆体领域无论是在低功耗/高速运作、资料保存能力与反覆操作下的可靠度表现上均有显著的提升,如图十五所整理各项新兴记忆体的重要参数比较[31],铁电记忆体极具有竞争优势,各方面的效能预期会持续成长。

未来仍须克服多晶态(polycrystalline)铁电薄膜在元件微缩所面临元件之间(device-to-device)或同一元件不同操作次数之间(cycle-to-cycle)之特性变异性(variability)问题,以符合大规模记忆体模阵列运作上的需求。

微缩时,每一个元件所包含的晶粒(grain)数量减少,而这些晶粒之晶粒尺寸、晶相分布(铁电性/非铁电性晶相比例)、方向性(orientation)、晶界(grain boundary)特性各不相同,故元件之间的变异性会随微缩而越加明显[23],以先进的物性分析技术进行材料微观组织的鉴别将会越来越重要。一个改善变异性的方向是减少晶粒尺寸至2-3 nm 并保持铁电性,如此可在微缩的元件内包含数百个晶粒并可因为数量较多的晶粒而使得不均匀性被平均后而趋于和缓。控制HfO 2 铁电层成长时的热制程可调整晶粒尺寸,提高降温速度就是实现较小晶粒尺寸的可行方式之一[10]。

▲图十五新兴记忆体与现有Flash 快闪记忆体特性参数比较表[31]

基于HfO 2 铁电材料之FeRAM 记忆体未来发展不仅在于元件微缩性,更在于可实现三维结构、甚至是多位元储存的可行性与前瞻性,在制程复杂性与成本上更具有优势。相较现有内嵌式快闪记忆体,FeFET 记忆体高速、低电压操作、无须设计升压电路控制wordline 等优点,是未来In-Memory Computing 架构中极具潜力的记忆体技术。

基于HfO 2 铁电材料之FeRAM 记忆体其endurance 预期可达到10 12 次,虽然距离商用型基于PZT 铁电材料之FeRAM 记忆体具有10 15 次的可操作次数仍有些差距,但持续挹注研发能量预期将能缩小两者差距。基于HfO 2 铁电材料之FeRAM 记忆体未来更具有发展,不仅在于元件微缩性,更在于可实现三维结构[32]、甚至是多位元储存[33-34] 的可行性与前瞻性。与DRAM 相较之下,FeRAM 结构类似,但高极化密度可使记忆胞面积更能有效微缩,因此在制程复杂性与成本上更具有优势[11]。

基于HfO 2 铁电材料之FeFET 记忆体,初期的市场定位在内嵌式记忆体非挥发记忆体(embedded nonvolatile memory)[35] 协助运算功能,与现有的内嵌式快闪记忆体(embedded flash memory)相较之下,FeFET 记忆体具有高速、低电压操作、无须设计升压电路(charge pumping circuit)控制wordline 等优点,因此极具有取代内嵌式快闪记忆体的潜力。

长远来看,迈向高密度储存应用的独立型(standalone)记忆体市场极具有潜力,原因在于单一记忆胞可储存3 个位元的技术已实现[13],且类似3D NAND Flash 快闪记忆体之垂直式FeFET 记忆体元件结构也成功展示[36-37],透过适当的技术整合是相当有机会的。另外,FeFET 记忆体在神经型态运算的系统中亦可扮演突触[38-39] 与神经元[40-41] 的角色,是未来In-Memory Computing 架构中极具潜力的记忆体技术。

铁电记忆体前景可期,期待早日完成策略布局

综观记忆体技术走向,随着「记忆体内运算」的发展,铁电记忆体不仅在先进制程、元件微缩,甚至多位元储存上,都具备可行性与前瞻性,也因此受到学界与业界的高度瞩目。虽然目前仍需克服耐受性上的不足,不过仍是未来记忆体内运算架构中,极具潜力的记忆体技术。

本篇原文作者清华大学巫勇贤教授,多年来致力于铁电记忆体的学术研究,其团队曾发表过许多重要的研究成果,皆已刊登于国际知名期刊,去年也获选为IEEE Electron Device Letters 的期刊封面与编辑精选。目前也与闳康科技进行产学合作,以其专业检设设备与技术,共同推动铁电记忆体研究发展。

然而,欲在铁电记忆体产业取得领先地位,除了于元件创新技术上须具备优势外,相关的电路与系统封装整合技术也是关键,也期待后续能看见台湾产官学界及早掌握契机,协力进行完整策略布局。

参考资料:

[1]. A. Mehonic et al., Adv. Intell. Syst., 2, 2000085 (2020)

[2]. J. Müller et al., ECS J. Solid State Sci. Technol., 4, N30 (2015)

[3]. SS Cheema et al., Nature, 580, 478 (2020)

[4]. TS Böscke et al., Appl. Phys. Lett., 99, 102903 (2011)

[5]. L. Xu et al., J. Appl. Phys., 122, 124104 (2017)

[6]. Z. Fan et al., J. Adv. Dielect., 6, 1630003 (2016)

[7]. RD Clark et al., ECS/AiMES Int. Meeting Within Symp., 1 (2018)

[8]. MH Park et al., Adv. Electron. Mater., 5, 1800522 (2019)

[9]. A. Toriumi et al., IEEE IEDM, 338 (2019)

[10]. B. Ku et al., IEEE Symp. VLSI Tech., TF2.5 (2020)

[11]. T. Mikolajick et al., J. Appl. Phys., 129, 100901 (2021)

[12]. N. Dahad, www.eetasia.com (website), (2020)

[13]. S. De et al., IEEE Symp. VLSI Tech., T7-2 (2021)

[14]. J. Müller et al., IEEE Symp. VLSI Tech., 25 (2012)

[15]. M. Pešić et al., Adv. Funct. Mater., 26, 4601 (2016)

[16]. W. Hamouda et al., J. Appl. Phys., 127, 064105 (2020)

[17]. JY Park et al., J. Appl. Phys., 128. 240904 (2020)

[18]. KY Chen et al., IEEE Symp. VLSI Tech., 84 (2017)

[19]. MG Kozodaev et al., J. Appl. Phys., 125, 034101 (2019)

[20]. L. Grenouillet et al., IEEE Symp. VLSI Tech., TF2.4 (2020)

[21]. M. Pešić et al., Adv. Funct. Mater., 26, 7486 (2016)

[22]. H. Mulaosmanovic et al., Nanotechnology, 32, 502002 (2021)

[23]. AI Khan et al., Nature Electronics, 3, 588 (2020)

[24]. E. Yurchunk et al., IEEE Inter. Reliability Physics Symp., 2E.5.1 (2014)

[25]. N. Gong et al., IEEE Electron Device Lett., 39, 15 (2018)

[26]. CY Chan et al., IEEE Symp. VLSI Tech., TF1.1 (2020)

[27]. AJ Tan et al., IEEE Electron Device Lett., 42, 994 (2021)

[28]. KY Chen et al., IEEE Symp. VLSI Tech., 119 (2018)

[29]. HK Peng et al., IEEE Electron Device Lett., 42, 835 (2021)

[30]. K. Ni et al., IEEE IEDM., 296 (2018)

[31]. V. Milo et al., Materials, 13, 166 (2020)

[32]. P. Polakowski et al., IEEE International Memory Workshop (IMW), (2016)

[33]. K. Lee et al., ACS Appl. Mater. Interfaces, 11, 38929 (2019)

[34]. K. Ni et al., IEEE IEDM., 669 (2019)

[35]. S. Slesazeck et al., IEEE ICICDT., 121 (2018)

[36]. F. Mo et al., IEEE Symp. VLSI Tech., 42 (2019)

[37]. MK Kim et al., Science Advances, 7, 1341 (2021)

[38]. M. Jerry et al., IEEE IEDM., 139 (2017)

[39]. CP Chou et al., ACS Appl. Mater. Interfaces, 12, 1014 (2020)

[40]. S. Dutta et al., IEEE Symp. VLSI Tech., T12-4 (2019)

[41]. C. Chen et al., IEEE Symp. VLSI Tech., T12-2 (2019)