随著 5G、IoT 与 AI 智慧时代持续引领终端应用,驱使 HPC 芯片逐步成为高阶产业于资料中心、深度学习与挖矿需求等领域训练与推论的重要发展关键。为求实现相关需求,高阶 2.5D / 3D IC 封装技术已是其中最佳解方,然而近年由于产品功能性和记忆体需求大增,间接影响相关封测技术发展,各主流大厂纷纷看到芯片与芯片间、逻辑芯片与存储芯片间信号沟通的重要性,对此提出相应的高阶 HPC 芯片封装主架构外,也尝试进一步运用小芯片 Chiplet 方式同步解决芯片间堆叠疑虑,期望改善信号传输效率和运算表现。

EDA加速HPC封装发展,台积电主打SoIC因应Chiplet需求

针对高阶2.5D / 3D IC封装技术,现行EDA厂商如Cadence等可支援相关线路配置、芯片间信号传输与散热等模拟应用,并提供现行主力IDM大厂、Foundry与OSAT厂于上游半导体设计至下游封测端的完整解方。因此于HPC芯片封装领域持续领先的Foundry龙头台积电,也运用EDA工具强化与加持,从2011年起推出首代CoWoS封装,以及近期将推出第四代产品,皆可见到相关工具身影。

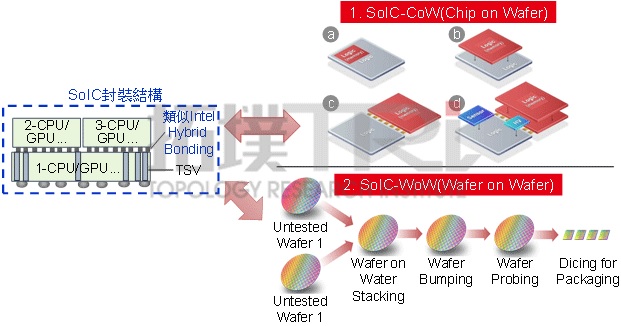

对此,现行Foundry龙头台积电于HPC芯片封装发展趋势,由于本身优异半导体制程微缩(5nm和7nm)与封装技术(Interposer和TSV等)能力,逐步吸引全球知名HPC芯片厂商于此投单。然而发展过程中,因单芯片系统SoC内区块间沟通与制程良率较难实现,因而驱使台积电尝试透过小芯片Chiplet的SoIC封装技术进行调整,并期望后续该技术将能进一步延伸应用于CoWoS与InFO等封装结构内且提升成效。

▲ 台积电SoIC封装主要设计理念与架构。(Source:台积电;拓墣产业研究院整理,2021.9)

与台积电较劲,英特尔与三星推Hybrid Bonding与X-Cube

为求因应台积电于高阶HPC芯片封装的主导地位,IDM大厂英特尔(Intel)与三星(Samsung)除了原先已拥有2.5D / 3D IC封装技术,也尝试针对小芯片Chiplet延伸封装技术进一步研制,诉求能与台积电SoIC技术一较长短。

以英特尔为例,由于本身拥有高阶HPC芯片(Co-)EMIB封装技术,结构试图透过其独到的Bridge结构架构为芯片间彼此沟通桥梁,并进一步针对小芯片Chiplet封装延伸,提出Hybrid Bonding结构,尝试改善逻辑芯片与存储芯片间堆叠情形,最终目标形成高速运算效能和优异传递架构。

三星部分,也因HPC芯片封装主要以I-Cube为发展主力,为求提升3D IC封装技术实力,已于2020年8月提出Chiplet延伸的X-Cube框架,期望透过结合I-Cube和X-Cube封装技术,提高现行HPC芯片厂商采用意愿。

来源:拓墣产业研究院