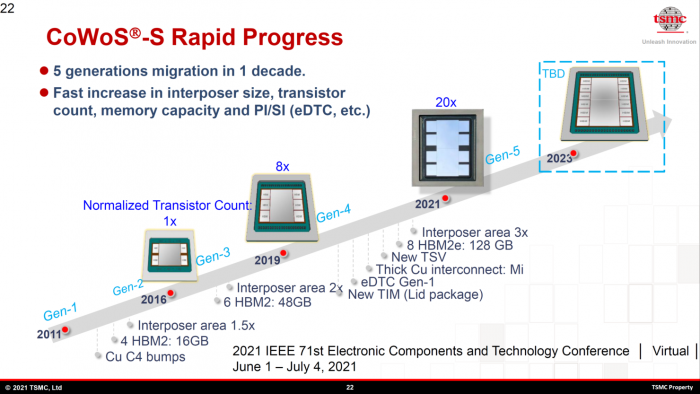

8月23日消息,在 HotChips33 年度会议期间,台积电介绍了CoWoS先进封装技术路线图。此外,台积电还展示了为下一代chiplet(小芯片,或称芯粒)架构和内存设计做好准备的最新一代 CoWoS 解决方案。

国外媒体WCCFTech 指出,作为业内领先的半导体巨头,台积电在先进芯片封装技术方面取得了快速进展。过去十年,该公司已经推出五代不同的基板上芯片封装工艺,且涵盖了消费级与服务器芯片领域。

根据规划,台积电将于今年晚些时候宣布第 5 代 CoWoS 封装技术,其有望将晶体管数量翻至第 3 代封装解决方案的 20 倍。

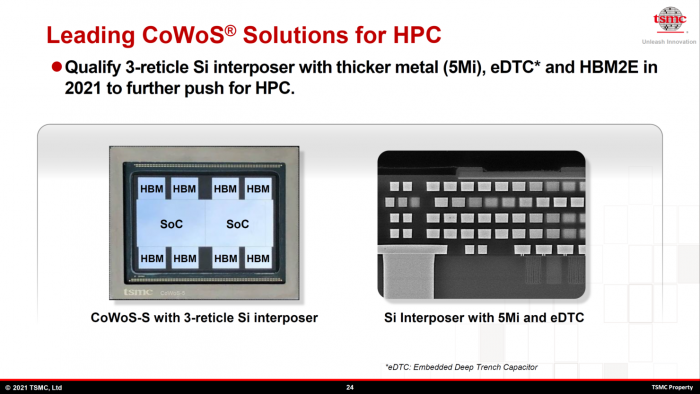

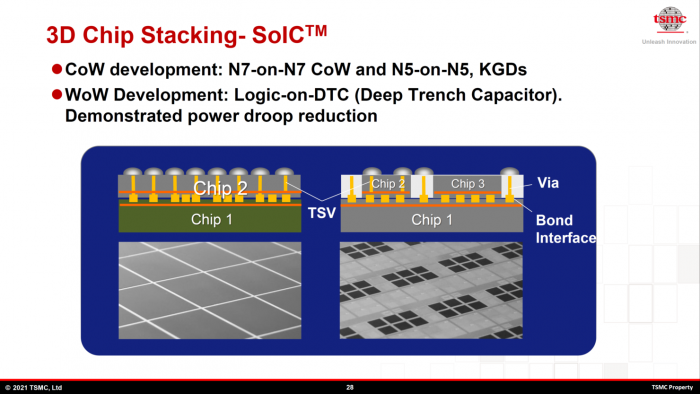

新封装将增加 3 倍的中介层面积、8 个 HBM2e 堆栈(容量高达 128 GB)、全新的硅通孔(TSV)解决方案、厚 CU 互连、以及新的 TIM(Lid 封装)方案。

其中最让我们关注的,莫过于使用台积电第 5 代 CoWoS 封装工艺的 AMD MI200“Aldebaran”GPU 。

作为 AMD 首款多芯片(MCM)设计的 GPU,其采用了 CDNA 2 核心架构,预计可实现一些疯狂的规格参数。

WCCFTech 指出,AMD“Aldebaran”GPU 或拥有超过 16000 个内核、以及高达 128GB 的 HBM2E 内存容量。

此外英伟达的 Hopper GPU 竞品也使用了 MCM 小芯片架构,且同样可能交由台积电代工。

至于第 5 代 CoWoS 封装技术能够为英伟达 Hopper GPU 带来怎样的惊喜,还请耐心等到 2022 年揭晓。

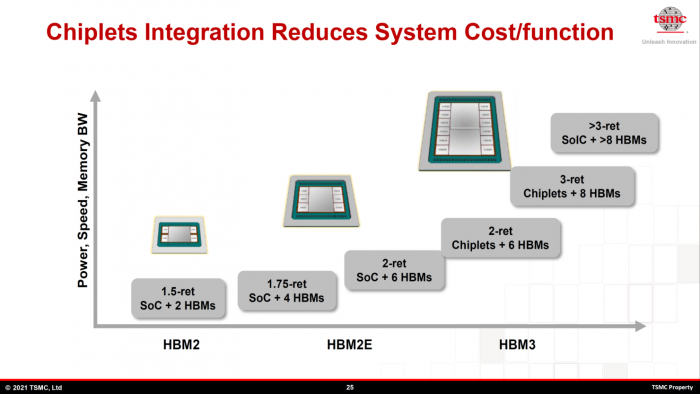

接着,TSMC 将升级到第 6 代 CoWoS 封装工艺,特点是能够集成更多的小芯片和 DRAM 内存。

台积电尚未敲定第 6 代 CoWoS 的最终工艺,但预计可在同一封装内容纳多达 8 组 HBM3 内存和 2 组计算小芯片。

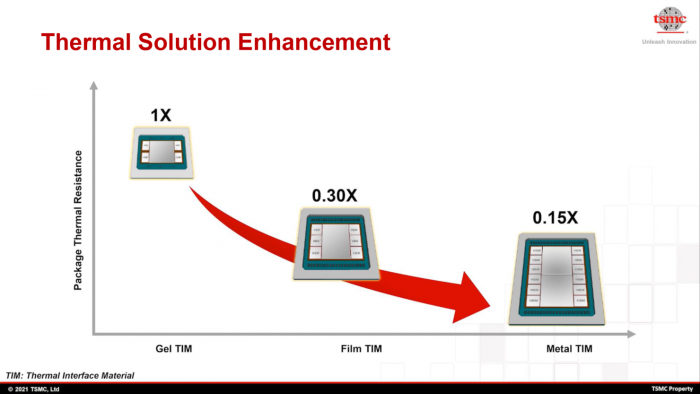

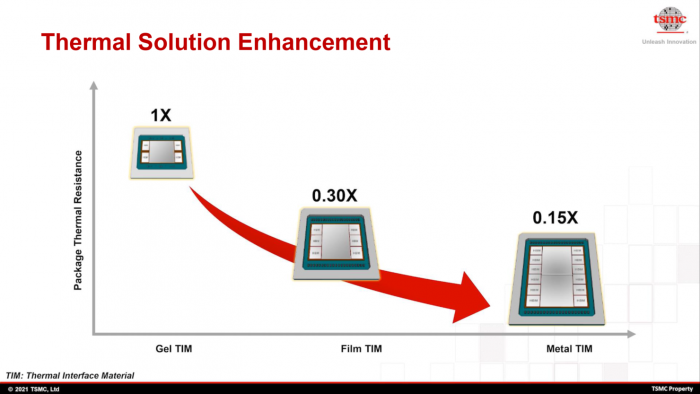

台积电还将以 Metal Tim 的形式,提供最新的 SOC 散热解决方案。

与初代 Gel Tim 方案相比,Metal Tim 有望将封装热阻降低到前者的 0.15 倍。

最后,AMD CNDA 3(MI300)和英伟达 Ampere 的下下一代,都有望采用 TSMC 的 N3 工艺节点进行制造。

来源:cnbeta