对于经历过SGI绘图工作站与Irix操作系统全盛时期的老一辈IT人,或着一路读着他们著作成长的科班人士,看到昔日高高在上的RISC诸神,继PA-RISC、Alpha、IA-64后(加上看似岌岌可危的SPARC),又将再消失一个,想必内心多少有股不胜唏嘘之感。

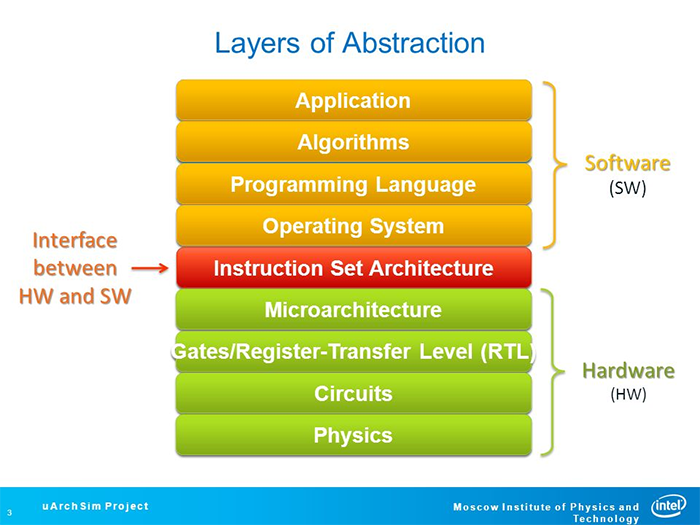

然后很可笑的是,几乎所有的媒体报导,都千篇一律耗费大量篇幅去解释「什么是指令集架构(ISA, Instruction Set Architecture),为什么这么重要」,仿佛计算机结构(Computer Architecture)一词由来过去数十年来从不存在,到今天才从天上掉下来。高谈阔论「RISC指令集的先天优势」就更好笑了,先别提这些老早就是教科书的基本知识,这些人是没看到20世纪末期是如何上映「RISC诸神的黄昏」吗?

言归正传。问世于2010年,由当代计算机结构大师David Patterson所领导的RISC-V(第五代RISC架构)指令集,因其开源与可自订客制化指令的特性,加上ARM自身节节高升的研发开销与营运成本,都羊毛出在羊身上的转嫁到授权费用,而NVIDIA企图并购ARM的举动,更进一步危及中立性。近期外传英特尔想以20亿美元代价并购SiFive、并确定将在2022年发表7nm制程、SiFive高效能核心Performance P550的Horse Creek处理器,更让RISC-V得到越来越多关注的目光。

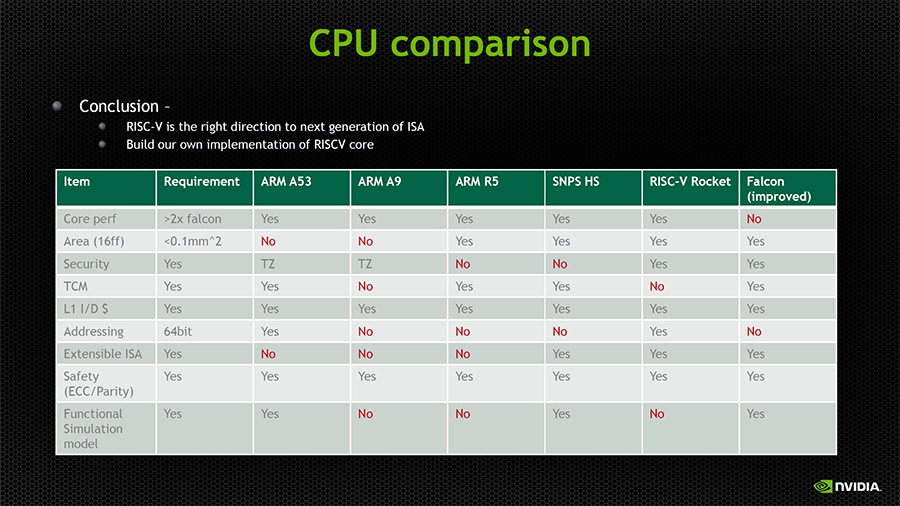

RISC-V早已得到科技大厂的青睐。NVIDIA从2016年,就在GPU内导入RISC-V指令集的Falcon(Fast Login Controller)微控制器,翻新使用超过十年的旧架构。

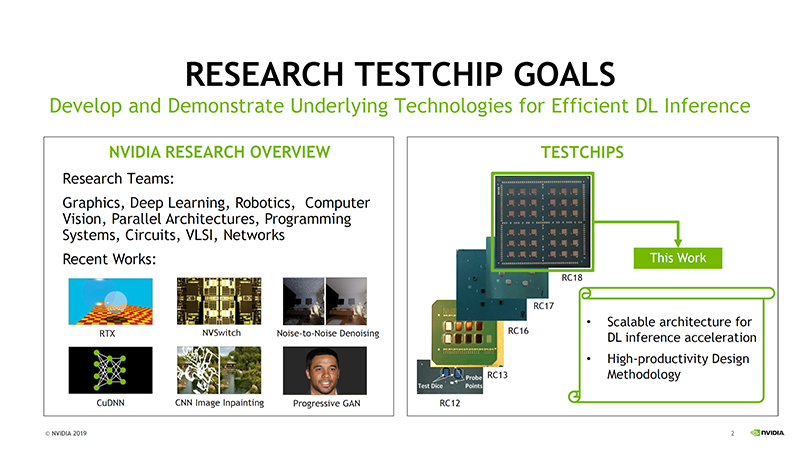

NVIDIA内部的RC18推论处理器研究案,也是整合RISC-V指令集相容处理器为I/O元件核心,实现每秒128兆次的推论执行,且功耗只有13.5瓦。

此外,Western Digital与Seagate这两间硬碟机双雄,也选择自研RISC-V处理器,作为新一代硬碟机/固态硬碟机的控制芯片,一年出货单位都以「10亿」起跳。David Patterson本人2016年加入Google,也让人不禁遐想,这间一向鸭子划水的云端巨头,是不是又要搞出啥惊天动地的大事。

即使RISC-V的发展看似前途似锦,但一般人可能还是对历史演进一头雾水,所以笔者就整理历届HotChips(及柏克莱大学内部教材)这个在处理器业界极具影响力的活动,并附上简报网址,方便各位瞧瞧RISC-V是怎么一步一步走过来的,又是如何展现应用多样性。

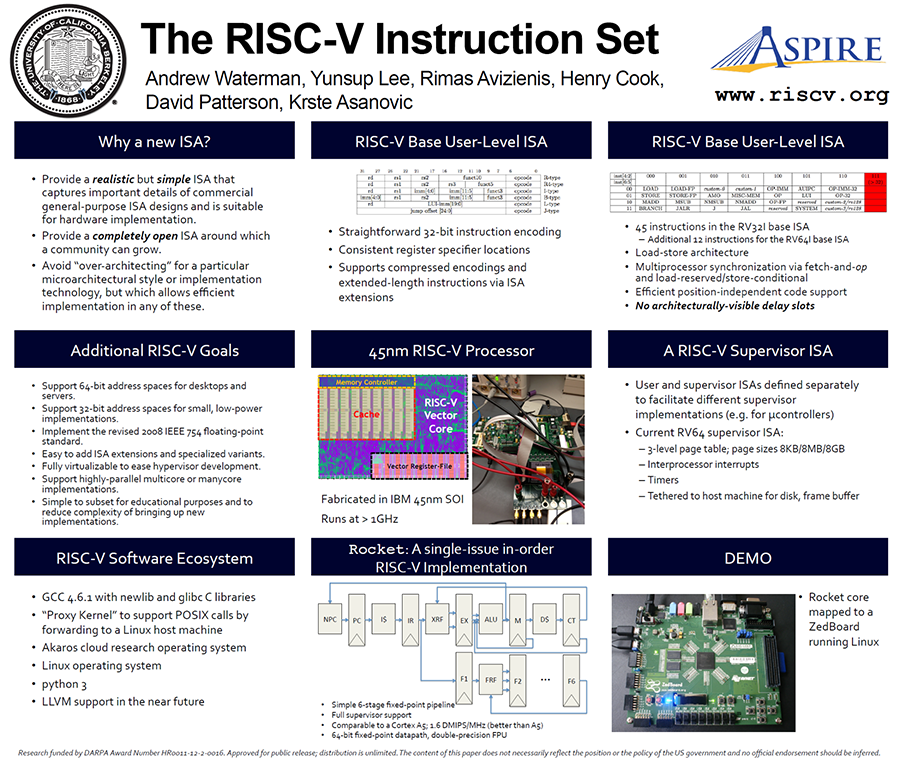

2013 HotChips 25

RISC-V首度在HotChips亮相,并展示基于IBM 45nm SOI晶圆制程的RISC-V处理器与「Rocket」实作微架构。值得一提的是,除了大名鼎鼎的David Patterson,成立于2015年的SiFive,三名创办人Krste Asanović、Yunsup Lee、Andrew Waterman均赫然在列。

(Source:The RISC-V Instruction Set)

2014 HotChips 26

这年RISC-V并未出现在活动议程,但他们还是留下这张照片。

(Source:Hotchips)

这届HotChips让笔者最有印象的,莫过于AMD的议程是有点搞笑的ARM版本Opteron「Seattle」。

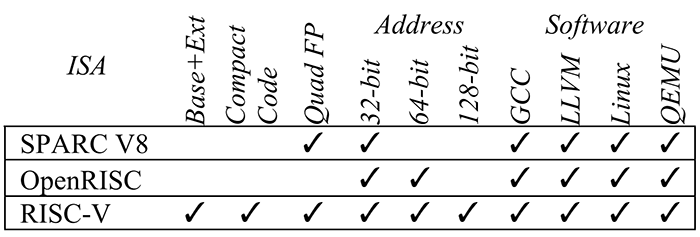

刚好在HotChips活动前,柏克莱大学出现这份教材,解释「为何指令集应该免费开放」,并且明示RISC-V相较其他开源RISC指令集的优势,包含预留定址模式、压缩指令编码版本和128位元定址等等。

(Source:Berkeley EECS)

2015 HotChips 27

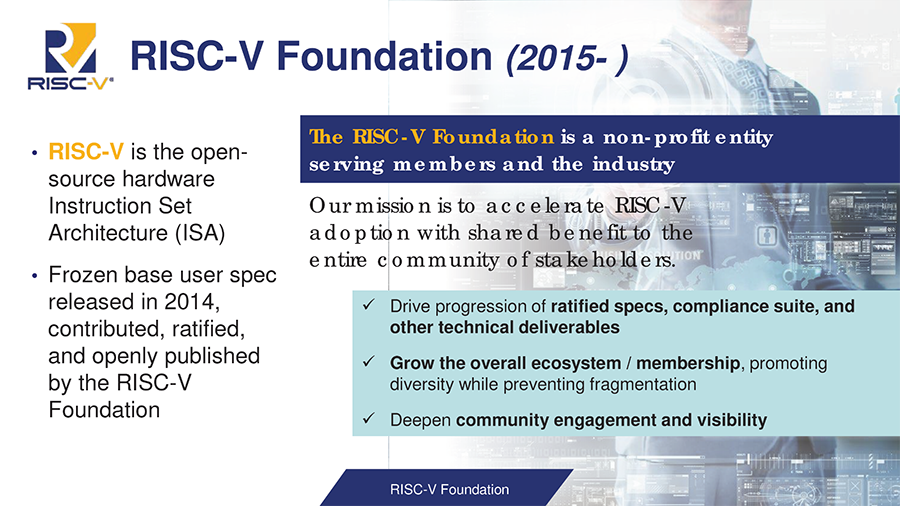

RISC-V基金会2015年正式成立。

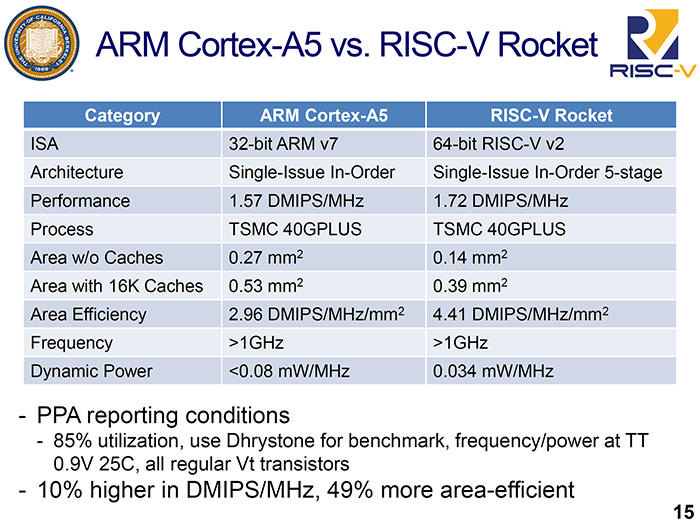

柏克莱大学实验性的28nm制程RISC-V向量处理器,不过重点还是摆在RISC-V相对ARM的优越性。

(Source:Hotchips)

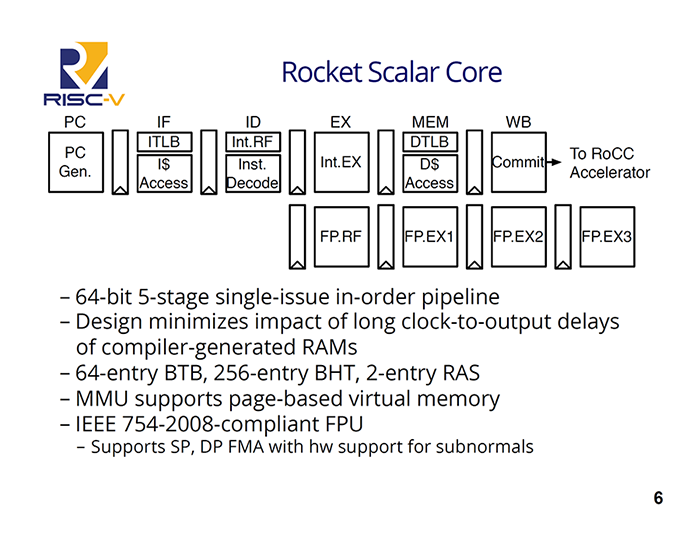

开源的Rocket纯量核心。NVIDIA第一代RISC-V Falcon就是以其为基础。

(Source:RISC-V)

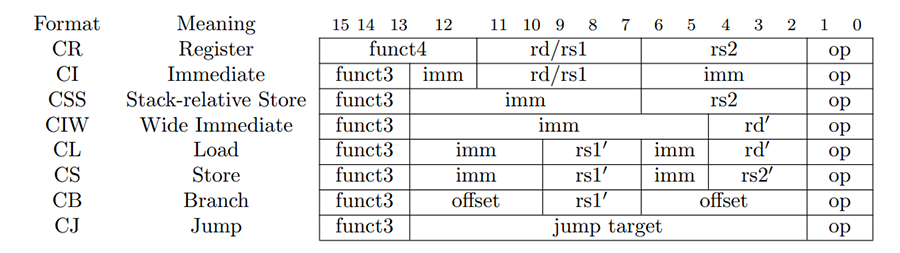

2015年底公布16位元指令编码长度的压缩版RISC-V规范,类似ARM的Thumb与MIPS的MIPS16。

(Source:RISC-V)

2017 HotChips 29

刚成立不久的SiFive发表业界第一颗开源的RISC-V芯片:Freedom E310微控制器,台积电180nm制程,面积6平方毫米。

(Source:Hotchips)

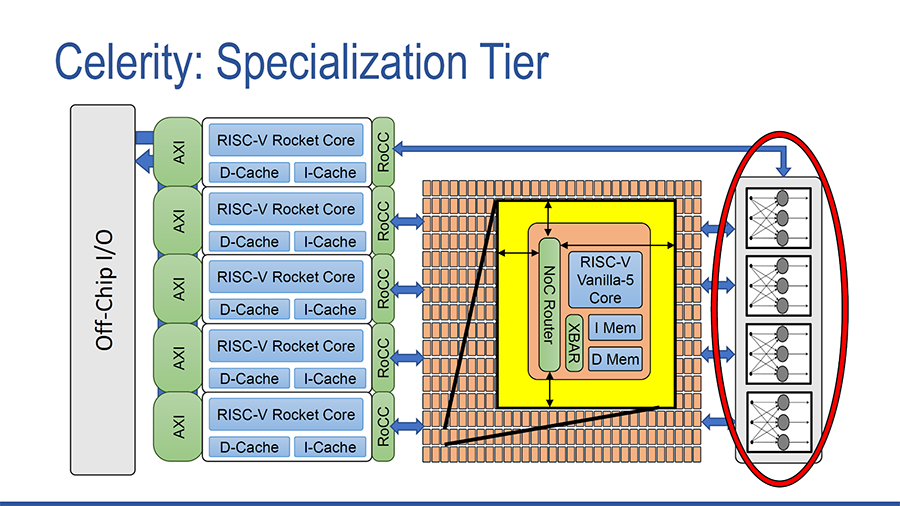

不限RISC-V的发迹地柏克莱大学,开始也有其他学校共襄盛举。

(Source:Hotchips)

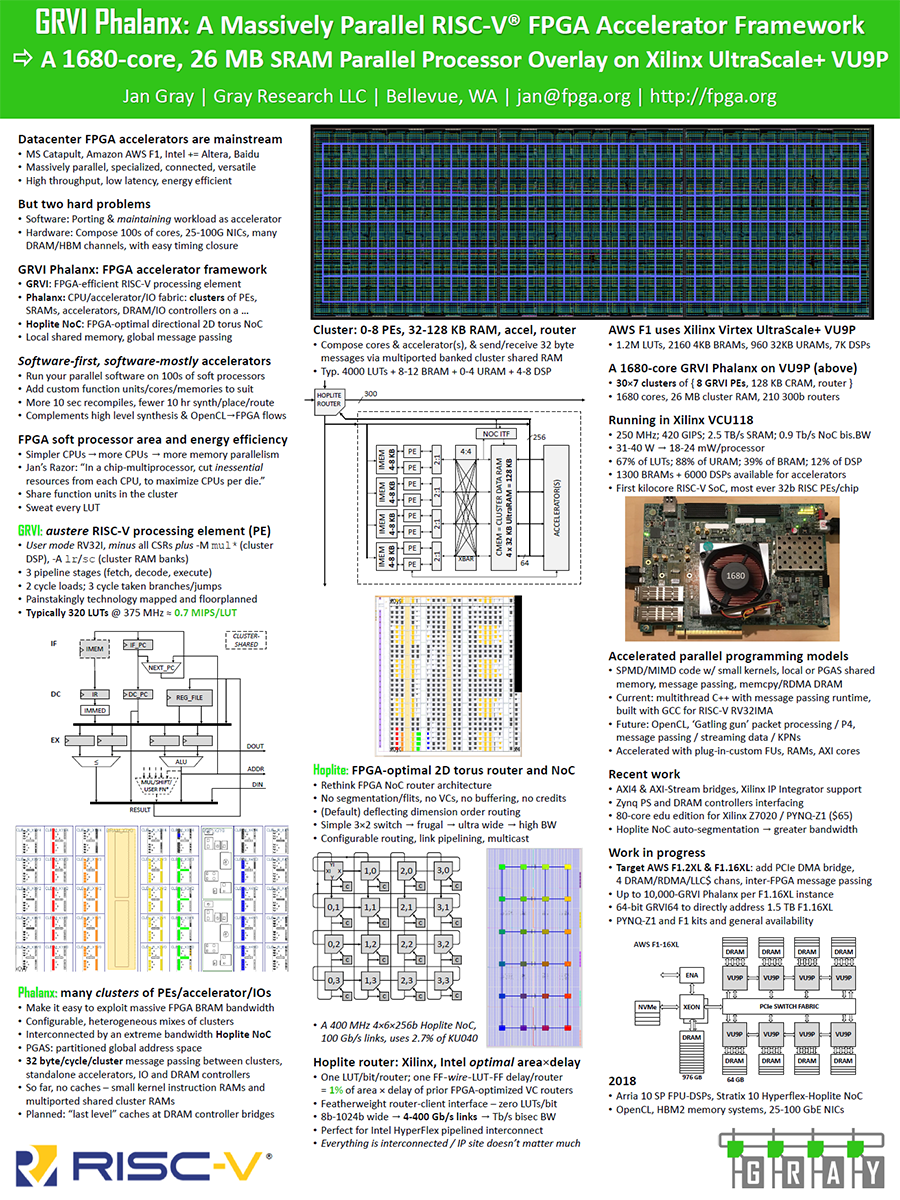

某间软硬体开发顾问公司用FPGA变出1680个RISC-V核心的参考设计框架。

(Source:Hotchips)

2019 HotChips 31

SiFive共同创办人讲解RISC-V的历史与全貌,并提及以2010年夏天「三个月即可实现的处理器专案」为起点,希望设计出更干净指令集架构的往事。

(Source:Hotchips)

介绍RISC-V的生态系统,姑且不论里面究竟有多少「水分」。

(Source:Hotchips)

2020 HotChips 32

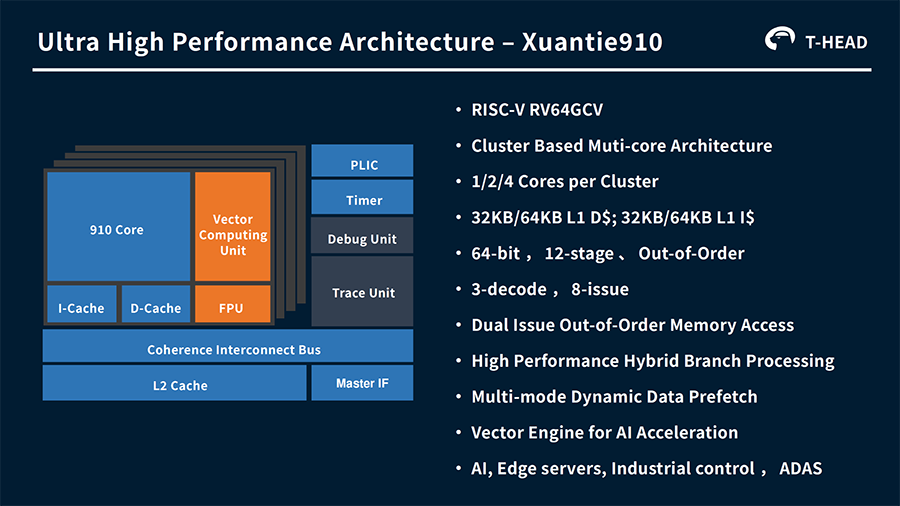

阿里巴巴也加入战局,研发针对人工智慧物联网(AIoT)的RISC-V芯片。

(Source:HotChips)

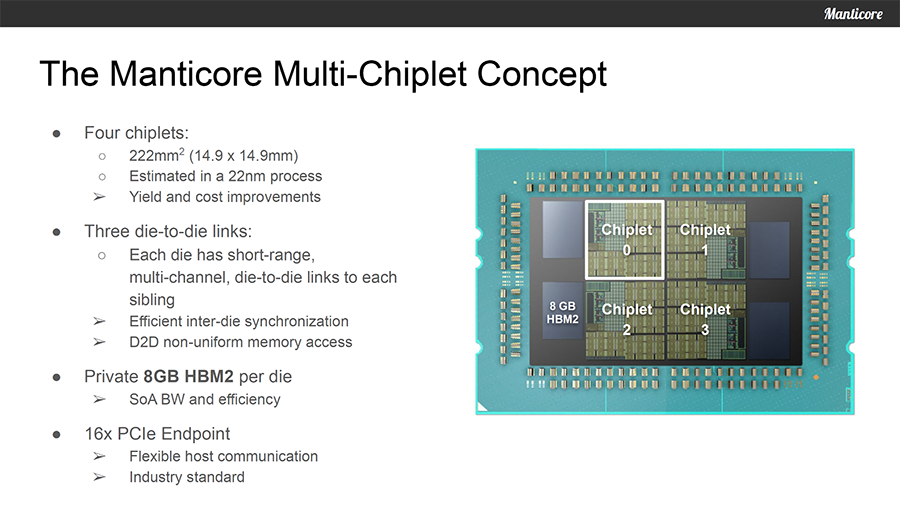

瑞士联邦政府1854年成立的研究机构,透过Chiplet多芯片“包水饺”,做出名为Manticore的4096核心怪物,目标在高效能浮点运算能比肩Fujitsu A64FX与NVIDIA A100。

(Source:HotChips)

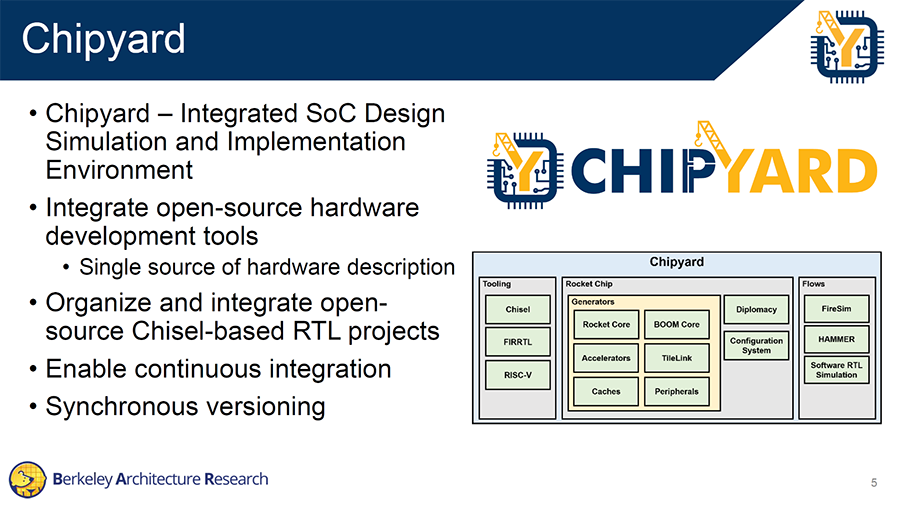

柏克莱大学研究的整合式系统单芯片设计模拟与实作环境。

(Source:HotChips)

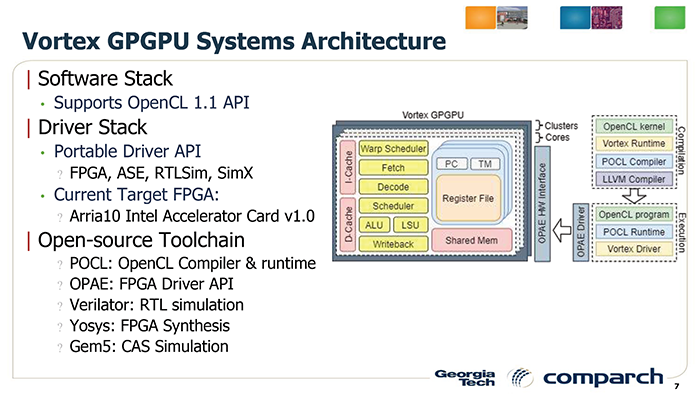

不限于CPU,美国理工大学排名前三名的乔治亚理工学院,也将RISC-V延伸到GPGPU应用。

(Source:HotChips)

2021 HotChips 33

以下是预定今年8月的HotChips 33议程,也许过一阵子会变得更多也说不定。

这也是学术研究案,目标在提升RISC-V处理器的安全性。

- Morpheus II: A RISC-V Security Extension for Protecting Vulnerable Software and Hardware(Todd Austin, University of Michigan)

RISC-V也开始「渗透」到开放式架构的5G基地台。

- Architecting an Open RISC-V 5G and AI SoC for Next Generation 5G Open Radio Access Network(Sriram Rajagopal, EdgeQ)

出现「Tensor」(张量)这关键字,对NVIDIA GPU不陌生的读者一定马上想起这是什么。

- Accelerating ML Recommendation with over a Thousand RISC-V/Tensor Processors on Esperanto\'s ET-SoC-1 Chip(David Ditzel, Esperanto Technologies)

基于「CORDIC」(座标旋转)的三角函数硬体加速器。

- A CORDIC-based Trigonometric Hardware Accelerator with Custom Instruction in 32-bit RISC-V System-on-Chip(Khai-Duy Nguyen; University of Electro-Communications)

这样一路看下来,相信各位大概知道一件事:对RISC-V最有兴趣的对象,无非「不想付钱给ARM,自己有本钱开晶片的大厂」、「想省掉ARM授权金,因此找免费方案的新创公司」、以及「连钱都没得付的学术机构」。

但即使RISC-V的发展势头,乍看之下「枝繁叶茂」差可比拟,但回到「RISC-V能否彻底取代ARM甚至x86」这个大哉问,笔者对此保持比较悲观的看法。天底下没有免费的午餐,当厂商充分享受针对特定应用而客制化指令集时,势必造成版本与软体分裂化,这也几乎注定RISC-V很容易变成「每个人自己玩自己的」,这对一套指令集的长期发展,绝对不是好事,要不然Linus Torvals也不会为了AVX-512暴走。

更何况也是最重要的,一套成功的指令集架构,如同「成功的男人背后都有一个伟大的女人」、「傲娇的公主身边都有一位万用的男人」,都有起码一个地位举足轻重的操作系统支撑存在价值,像x86有Windows,ARM有Android,那RISC-V呢?目前看不出来,但Google的态度可能是最重要的关键。

看在David Patteron已在Google工作的份上,是不是足以取代现有英特尔、AMD、IBM的高效能RISC-V泛用处理器,是不是已经在Google资料中心某排机柜内默默服役了?Google是否也看坏ARM的未来,为此主动「加码」RISC-V?这一切还很有得瞧。

来源:Technews 作者:痴汉水球