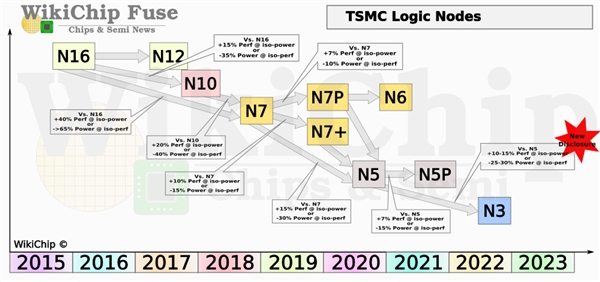

很快台积电的5nm工艺即将量产,与此同时,台积电的3nm工艺也在持续推进当中。去年7月,台积电就公开表示其 3nm 工艺的开发进展顺利,并且已经与早期客户就技术定义进行了接触。近日,台积电正式披露了其最新3nm工艺的细节详情,其晶体管密度达到了惊人的2.5亿个/mm²!

根据资料显示,基于台积电7nm EUV工艺的麒麟990 5G尺寸为113.31mm²,晶体管为103亿个,平均下来是0.9亿个/mm²,而台积电的3nm工艺则可将晶体管密度提升到2.5亿个/mm²。在性能提升方面,台积电5nm工艺相比7nm性能可提升15%,能效比提升30%,而3nm较5nm性能则可进一步提升7%,能效比提升15%。

另外,台积电在评估多种选择后认为现行的FinFET工艺在成本及能效上更佳,所以3nm首发依然会是FinFET晶体管技术。而三星则将会淘汰FinFET晶体管直接使用GAA环绕栅极晶体管,并且已经在GAA环绕栅极晶体管技术上取得了突破。不过,根据最新的消息显示,受今年新冠疫情的影响,三星的3nm工艺的进度可能将推迟。而台积电则表示,其3nm工艺研发符合预期,并没有受到疫情影响,预计在2021年进入风险试产阶段,2022年下半年量产。

编辑:芯智讯-林子

0