5月7日,英国系统级芯片(SoC)内部分析及监测技术供应商UltraSoC在深圳召开媒体发布会,介绍了其针对嵌入式CPU的监测和分析基础架构技术,同时推出了首款针对RISC-V的周期精确追踪技术IP,可支持高性能计算、存储和实时设备的设计人员能够从其产品中获取最高级别的性能。同时,通过增加周期精确的追踪功能,可使利用UltraSoC嵌入式分析技术的实时应用开发人员不仅能够查看器件内部发生的情况,而且更为关键的是可以看到发生某些情况的时间。

▲UltraSoC CEO Rupert Baines

支持异构多核SoC加速设计

随着应用的越来越复杂,对于芯片的性能、能效、功耗的要求也是越来越高,芯片的设计也变得越来越复杂,比如一颗高端手机芯片当中可能含有上百亿个晶体管,并且有着多核,异构的架构,那么如何确保SoC芯片在流片之前,解决各种硬件BUG,使得其内部的每个部分都能够实现既定的性能指标和效果呢?这就需要有一套可以对SoC内部提供精确分析及监测的技术。

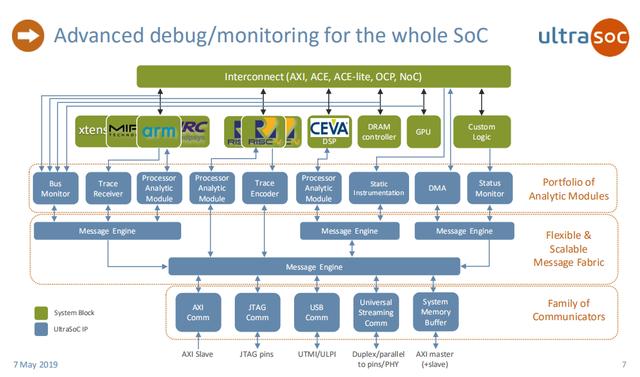

UltraSoC就是一家专为系统级芯片(SoC)提供内部分析及监测技术的企业。客户只需在芯片设计时将UltraSoC的硬件IP嵌入到SoC中,即可直接获取SoC内部各个部分活动的原始数据。更为重要的是,UltraSoC的技术不仅可以支持多核,还可支持多种不同类型的处理器(比如MIPS/Arm/RISC-V/CEVA/DRAM/GPU/定制的逻辑),即可支持异构多核,放在同一个系统当中进行整合。UltraSoC针对不同类型的处理器都有对应的模块进行数据采集,汇集,统一处理,然后进行数据导出。

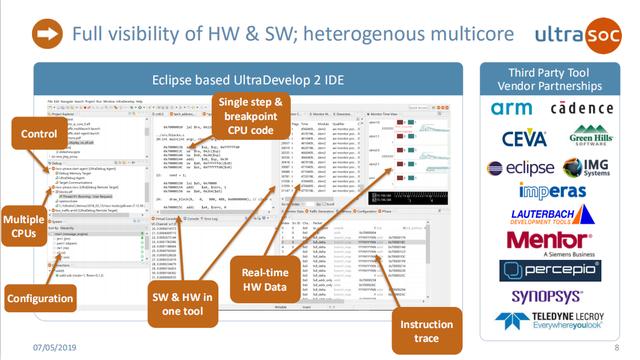

同时UltraSoC还有配套的基于开源的Eclipse开发的可视化集成开发环境工具UltraDevelop 2,可以快速的将获取到的原始数据处理成为工程师能够看懂的信息,并提供改善意见。UltraSoC将其称之为工程师直接与硬件沟通的渠道,这种集成软硬一体的开发界面,可以帮助工程师更快的调试芯片。

值得一提的是,UltraSoC的第三方开发工具合作伙伴还包括Arm、Synopsys、Cadence、CEVA、Mentor等。

降低成本、功耗,提升安全性

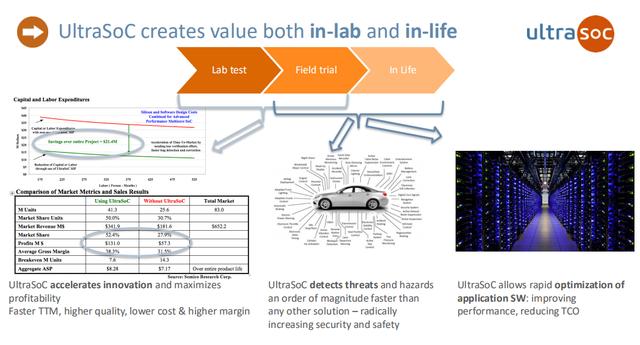

UltraSoC CEO Rupert Baines表示,其SoC内部分析及监测技术可以助企业更好地应对不断升级的系统复杂性难题,同时可以通过更快速的错误检测和纠正来加快上市时间,从而降低成本,提升产品竞争力。

根据UltraSoC公布的数据显示,以一颗7nm的芯片研发为例,采用UltraSoC的技术将可帮助整个芯片设计项目节省超过2000万美金的成本。

此外,在SoC量产大规模应用之后,客户仍然可以通过UltraSoC的嵌入式分析IP对于SoC进行持续的监测和分析,因为很多问题的发现都是在大批量出货之后。客户可以根据发现的问题,通过软件进行修改和优化,通常可以带来10-20%的性能提升,同时功耗也会得到进一步降低。

Rupert Baines表示其嵌入式分析IP可以在SoC的从设计到商用整个生命周期内都能够提供价值。

在安全性方面,UltraSoC的嵌入式分析技术将“智能”IP嵌入到SoC中,可以全面了解所有硬件和软件,监控和分析所有信息流、内存访问和网络流量,识别异常行为变化或非法操作。这是基于硬件的技术,因此难以颠覆或篡改,这也使得SoC在网络安全以及功能安全上得到提升。

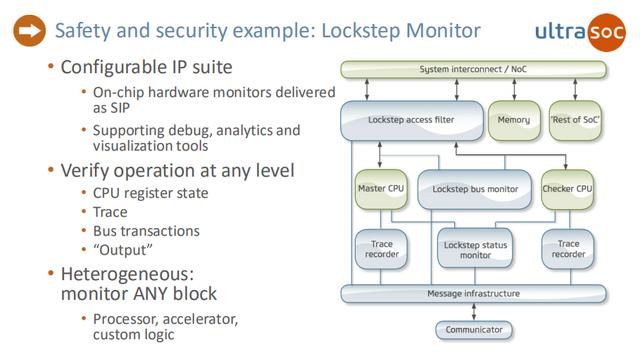

此外,对于安全性要求更高的应用来说,UltraSoC去年也推出了一种基于硬件的可扩展解决方案——UltraSoC Lockstep Monitor锁步监测器,支持所有常见的锁步/冗余架构,包括双冗余锁步、分离/锁定、主系统/核查器、以及利用任意数量内核或子系统投票等全部模式。

UltraSoC Lockstep Monitor具有协议感知功能,且可用于在两个或多个冗余系统之间完成输出、总线繁忙度、代码执行、乃至寄存器状态的交叉检查。它可以用于任何处理器架构,包括诸如新兴的RISC-V结构等那些对锁步配置缺乏原生支持的处理器架构。除了传统的处理器内核,它还可以检查其他子系统或加速器。因为它是在硬件中实现的,所以它能以线速完成响应并且不会为主系统带来任何能耗负担。

与传统方法不同,UltraSoC Lockstep Monitor锁步监测器包含灵活的、运行时可配置的嵌入式智能,从而支持系统级芯片(SoC)设计人员根据应用精确地定制监测和响应系统。监测功能可以在各种细节层次上实现:在子系统级别(比较两个处理器的输出),在指令交互级别(例如比较总线流量),使用UltraSoC的高级指令跟踪功能实现指令级别,以及通过检查内部状态或者寄存器内容在最底层的硬件级别实现。

UltraSoC Lockstep Monitor锁步监测器可以支持任何处理器架构或其他子系统,包括自定义逻辑或加速器。许多安全标准都要求锁步操作,例如汽车领域的ISO26262、以及IEC 61508、EN50126 / 8/9和CE 402/2013。

据介绍,自2015年成立至今,UltraSoC的SoC内部分析及监测技术已经得到了华为海思、Seagate、 Kraftway、C-SKY(中天微)/阿里巴巴平头哥, Andes, Esperanto等众多合作伙伴的采用。并且很多合作伙伴都将其应用到了RISC-V芯片的设计当中。

在AI&ML方面,通常都需要分析或学习大量的数据,UltraSOC的嵌入式分析IP可以对SoC内所产生的大量的数据进行分析和监测,可以监测到异常的AI&ML数据,自动查找Bug,告诉工程师应该检查那个部分,提升效率。

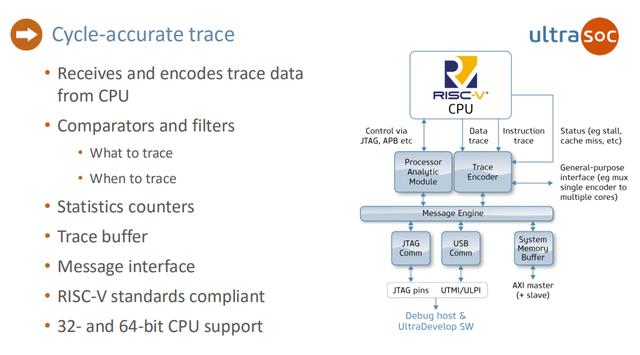

发布首款针对RISC-V的周期精确的商用追踪编码器IP

在很多实时和性能关键型(performance-critical)应用中,周期精确追踪正变得越来越重要,工程师需要将其硬件和软件代码的运行优化到单时钟周期的水平,即被CPU、GPU、DSP或加速器所识别的最小时间单位。周期精确追踪技术最初将作为UltraSoC用于RISC-V处理器追踪解决方案的一部分提供,RISC-V是一个快速增长的开源处理器项目。

“挤出最多可用的每一点性能正变得越来越重要,”Ultrasoc首席技术官Gajinder Panear说:“在‘每个周期都有价值’的世界中,我们正在力助推进更快的数据访问、更好的计算性能和最佳效率。”

由于UltraSoC的分析和监测技术被直接嵌入到芯片的硬件中,因此与使用其他技术相比,它能够捕获SoC中更快发生的事件(通常在纳秒级的范围内)。访问这种周期精确的追踪信息意味着致力于深度嵌入式应用的客户将能够准确地查看他们的代码执行的周期数,是否存在停顿和依赖关系,以及它们持续了多长时间。 掌握了这些信息,这些性能关键型系统的设计人员可以进一步优化其设计并获得最大的效率收益。

UltraSoC推出了新的周期精确追踪功能,建立于UltraSoC在RISC-V开发和调试方面的领先性基础之上。 在2018年初,该公司宣布推出业界第一款也是唯一一款专为RISC-V设计的商用追踪编码器IP,提供了一种实时监控CPU程序执行的机制。 它对指令执行和数据内存访问进行编码(可选),并输出一种高度压缩的追踪格式。 外部软件可以随后获取此数据并使用它来重建程序执行流程。 UltraSoC的RISC-V追踪编码器是为符合RISC-V标准而开发的,同时提供许多强大的功能,如数据和指令追踪、一系列计数器和定时器以及快速分析描绘工具,使其与实现基线RISC-V标准要求的开源代替产品明显不同。

由于与其他内核的软件、外围设备、实时事件、不成熟集成或上述所有因素的某种组合形成交互,软件的运行并不总是如预期的那样或在预期时候的那样运行;结果是实时行为受到了影响。处理器追踪是系统开发人员的一个关键需求,因为它支持详细地查看程序的运行,逐条指令的周期精确追踪允许您查看程序是在何时被执行的。UltraSoC的RISC-V Trace Encoder追踪编码器支持32位和64位RISC-V设计,该IP块可与UltraSoC产品组合的其他部分顺利集成,支持开放式和行业标准架构,以将自分析功能置于SoC的核心。

UltraSoC CEO Rupert Baines表示其非常看好未来RISC-V的发展前景,因此也是率先针对RISC-V推出周期精确的商用追踪编码器IP。值得一提的是,UltraSoC也是 RISC-V 联盟的活跃成员。

编辑:芯智讯-浪客剑