本周,西部数据(Western Digital)针对其去年推出的RISC-V处理器计划发布了三项重要公告,公布了基于RISC-V指令集的自研通用架构SweRV和开源的SweRV指令集模拟器(ISS),以及基于以太网OmniXtend的缓存一致性技术。

西部数据预计硬件和软件将用于大数据和快速数据应用的各种解决方案,包括闪存控制器和SSD。

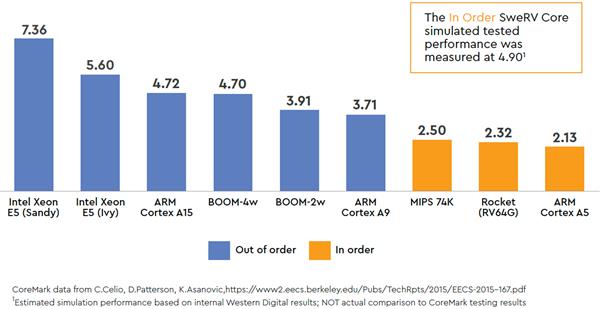

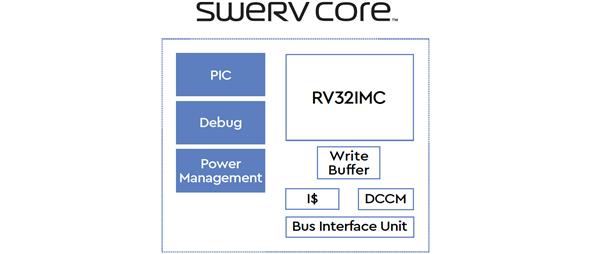

西部数据的SweRV架构是一个32bit顺序执行架构,具有双向超标量设计和9级流水线,采用28nm工艺技术实现,运行频率高达1.8GHz,可提供4.9 CoreMark/MHz的模拟性能,略高于Arm的Cortex A15架构。西

部数据将从2019年第一季度开始将其作为开源产品提供给第三方,希望通过第三方的使用,推动硬件和软件开发人员最终采用RISC-V指令集。

同时西部数据还推出了开源的SweRV指令集模拟器(ISS)。该程序使软件设计人员能够在SweRV内核上模拟其代码的执行,简化程序的开发,这对于推动RISC-V的采用非常重要。

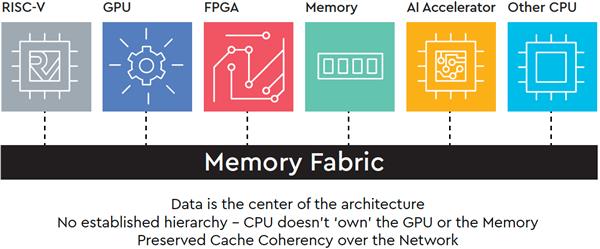

除了自己的处理器架构和指令集模拟器外,西部数据还推出了与SiFive共同开发的OmniXtend缓存一致性技术,该技术可实现以太网上的缓存一致性。

西部数据希望这一技术可以为处理器附加非易失性内存,但同时表示这种以内存为中心的架构也可用于CPU、GPU、FPGA和机器学习加速器等其他组件。

西部数据没有公开OmniXtend可提供的最大带宽,但是应该不会比现有的各版本以太网慢。

虽然OmniXtend是开源的,并且可供各方使用,但上述组件(加速器和处理器等)的开发人员是否真正决定使用OmniXtend当然还有待观察。

0